# EC 230 LOGIC CIRCUIT DESIGN LAB

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

# Vision

To nurture the talents of electronics and communication engineers, making them highly competent for growth of the society.

# Mission

- To deliver excellence in teaching learning process.

- Promote safe, orderly, caring and supportive environment to learners.

- Development of skilled engineers to perform innovative Research for betterment of the society.

- To encourage industry institute interaction, career advancement, innovation and entrepreneurship development.

# **Program Educational Outcome (PEO)**

- PEO1: To acquire a strong foundation in mathematics and scientific fundamentals, to develop an ability to analyze various functional elements of different disciplines of electronics and communication engineering.

- PEO2: Develop technical competence to move in pace with rapid changes in technology.

- PEO3: Equip learners to strengthen knowledge and soft skills for carrier advancement.

- PEO4: Adhere to ethics to contribute for betterment of the society.

# **Program Specific Outcomes (PSO)**

- PSO1. To understand principles and applications of various electronic components/devices and circuits.

- PSO2. Enable learners to solve complex problems using modern hardware and software tools.

| OURSE<br>CODE            | COURSE NAME                                                                                                                                                         | L-T-P-<br>C            | YEAR OF<br>INTRODUCTION     |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------|

| EC230                    | LOGIC CIRCUIT DESIGN LAB                                                                                                                                            | 0-0-3-1                | 2016                        |

| Prerequisite:            | EC207 Logic circuit design                                                                                                                                          | <u> </u>               |                             |

| Course object            | ives:                                                                                                                                                               |                        |                             |

| • To stud                | ly the working of standard digital ICs and                                                                                                                          | basic buildin          | g blocks                    |

| • To desi                | gn and implement combinational circuits                                                                                                                             |                        |                             |

| • To desi                | gn and implement sequential circuits                                                                                                                                |                        |                             |

| List of Experi           | ments: (Minimum 12 experiments are t                                                                                                                                | to be done)            |                             |

|                          |                                                                                                                                                                     |                        |                             |

| 1. Realiza               | tion of functions using basic and universa                                                                                                                          | al gates (SOP          | and POS forms).             |

|                          | and Realization of half /full adder and su                                                                                                                          | btractor using         | g basic gates and universal |

| gates.<br>3. 4 bit ad    | der/subtractor and BCD adder using 7483                                                                                                                             | 2                      |                             |

|                          | binary comparator.                                                                                                                                                  |                        |                             |

|                          | to Gray and Gray to Binary converters.                                                                                                                              |                        |                             |

| •                        | of Flip Flops: S-R, D, T, JK and Master S                                                                                                                           | ave IK FF us           | ing NAND gates              |

|                          | aronous Counter: Realization of 4-bit cour                                                                                                                          |                        | ing f (f in (D) gates       |

| •                        | ronous Counter: Realization of Mod-N co                                                                                                                             |                        |                             |

| 10. Synchr<br>11. Synchr | ronous Counter:3 bit up/down counter<br>onous Counter: Realization of 4-bit up/do<br>onous Counter: Realization of Mod-N cou<br>onous Counter:3 bit up/down counter | wn counter.<br>inters. | ents.ii                     |

| -                        | egister: Study of shift right, SIPO, SISO,                                                                                                                          | PIPO, PISO (           | (using FF & 7495)           |

| 14. Ring co              | ounter and Johnson Counter. (using FF &                                                                                                                             | 7495)                  | -                           |

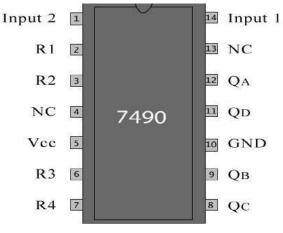

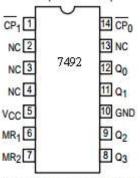

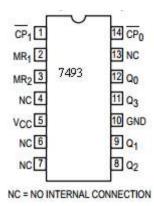

| 15. Realiza              | tion of counters using IC's (7490, 7492, 7                                                                                                                          | 7493).                 |                             |

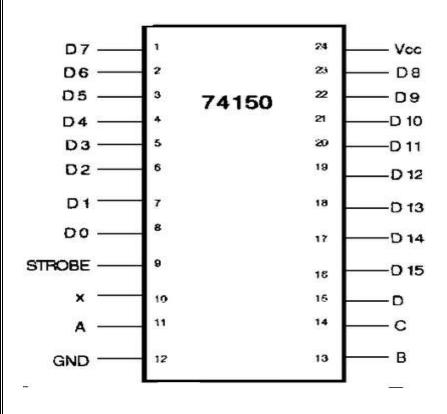

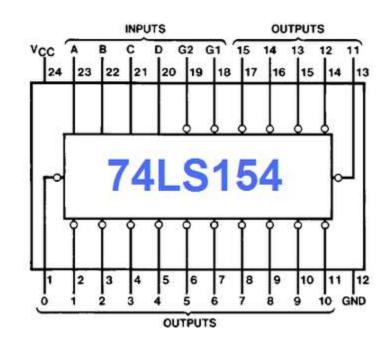

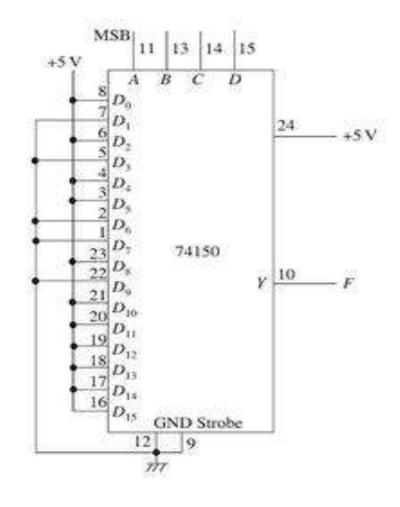

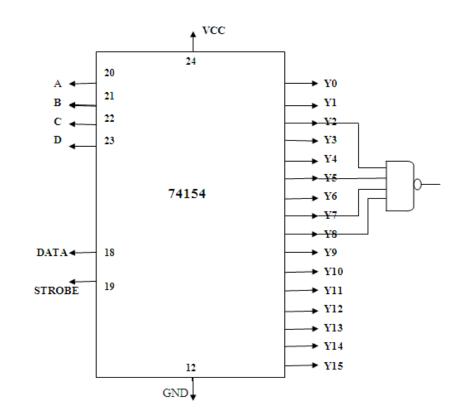

| 16. Multip               | exers and De-multiplexers using gates an                                                                                                                            | d ICs. (74150          | ), 74154),                  |

| 17. Realiza              | tion of combinational circuits using MUX                                                                                                                            | K & DEMUX              |                             |

| 18. Randor               | n sequence generator.                                                                                                                                               |                        |                             |

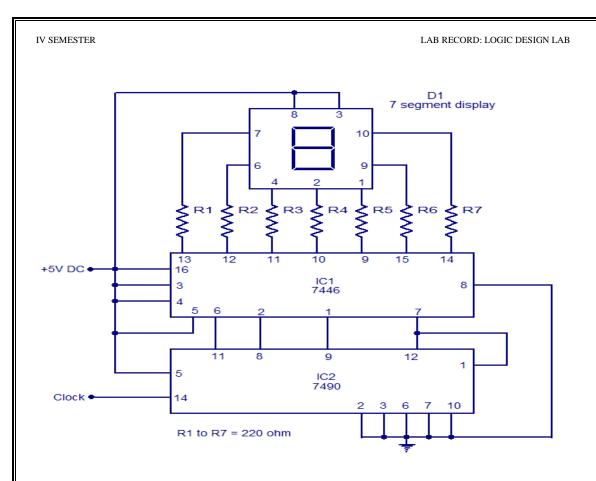

| 19. LED D                | isplay: Use of BCD to 7 Segment decode                                                                                                                              | r / driver chip        | to drive LED display        |

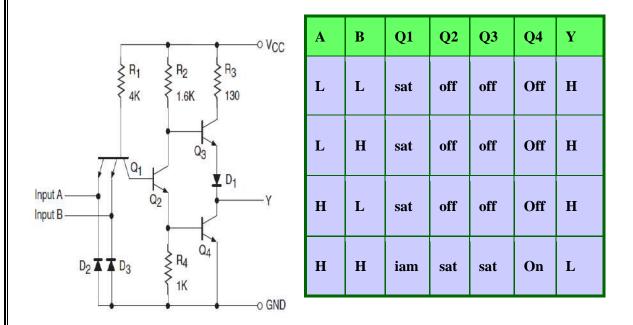

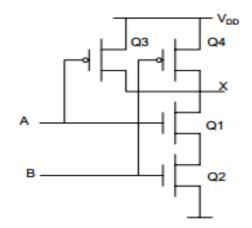

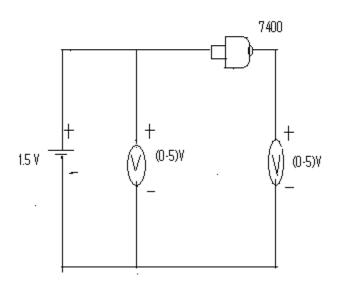

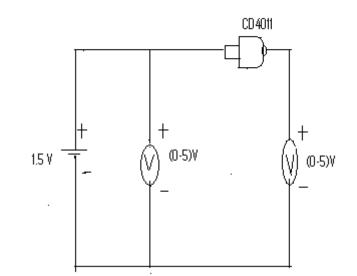

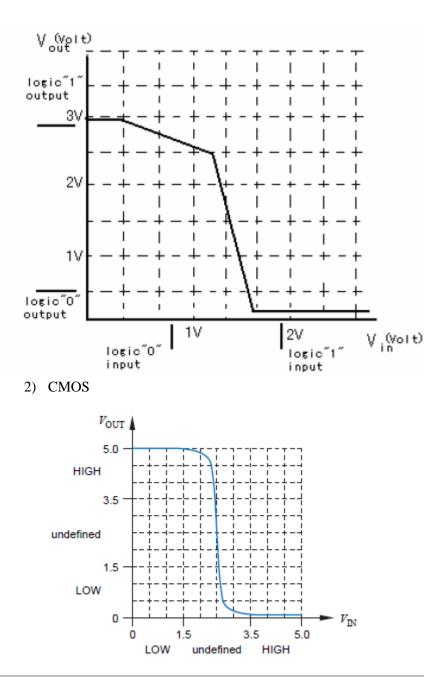

| 20. Static a             | nd Dynamic Characteristic of NAND gat                                                                                                                               | e (MOS/TTL)            | )                           |

| Expected outo            | come:                                                                                                                                                               |                        |                             |

| The student sh           |                                                                                                                                                                     |                        |                             |

| 1. Design                | and demonstrate functioning of various c                                                                                                                            | ombination c           | ircuits                     |

| 2. Design                | and demonstrate functioning of various s                                                                                                                            | equential circ         | uits                        |

| 3. Function              | on effectively as an individual and in a tea                                                                                                                        | m to accomp            | ligh the given tool         |

## EC 230 - LOGIC CIRCUIT DESIGN LAB

## COURSE OUTCOME, CO-PO MAPPING

| C230.1 | The students will be able to demonstrate the function of standard digital ICs and      |

|--------|----------------------------------------------------------------------------------------|

|        | basic building block                                                                   |

| C230.2 | The students will be able to do the design and implementation of combinational         |

|        | circuits.                                                                              |

| C230.3 | The students will be able to do the design and implementation of sequential circuits.  |

| C230.4 | The students will be able to function as an individual and in a team to accomplish the |

|        | given task.                                                                            |

| CO/  | РО | PO | PO | PO | PO | PO | РО | PO | PO | PO | PO | РО | PSO | PSO |

|------|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|

| PO   | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 1   | 2   |

| EC2  | 2  | -  | -  | -  | -  | -  | -  | -  | 2  | -  | -  | 2  | 2   | -   |

| 30.1 |    |    |    |    |    |    |    |    |    |    |    |    |     |     |

| EC2  | 2  | -  | -  | -  | -  | -  | -  | -  | 3  | -  | -  | -  | 3   | -   |

| 30.2 |    |    |    |    |    |    |    |    |    |    |    |    |     |     |

| EC2  | 2  | -  | -  | -  | -  | -  | -  | -  | 3  | -  | -  | -  | 3   | -   |

| 30.3 |    |    |    |    |    |    |    |    |    |    |    |    |     |     |

| EC2  | -  | -  | -  | -  | -  | -  | -  | -  | 3  | -  | -  | -  | -   | -   |

| 30.4 |    |    |    |    |    |    |    |    |    |    |    |    |     |     |

# **LIST OF EXPERIMENTS**

- 1. FAMILIARIZATION OF LOGIC GATES

- 2. IMPLEMENTATION OF GIVEN BOOLEAN EXPRESSION USING LOGIC GATES IN SOP AND POS FORMS

- 3. DESIGN AND IMPLEMENTATION OF ARITHMETIC CIRCUITS

- 4. BIT ADDER/SUBTRACTOR AND BCD ADDER USING 7483

- 5. 2/3 BIT BINARY COMPARATOR

- 6. BINARY TO GRAY AND GRAY TO BINARY CONVERTERS

- 7. FLIP FLOPS

- 8. ASYNCHRONOUS COUNTERS

- 9. SYNCHRONOUS COUNTERS

- **10. RANDOM SEQUENCE GENERATOR**

- **11. SHIFT REGISTERS**

- **12. RING COUNTER AND JOHNSON COUNTER**

- 13. REALIZATION OF COUNTERS USING IC'S(7490,7492,7493)

- 14. MULTIPLEXERS AND DEMULTIPLEXERS USING GATES AND ICS(74150,74154)

- 15. REALIZATION OF COMBINATIONAL CIRCUITS USING MUX AND DEMUX

- 16. USE OF BCD TO 7 SEGMENT DECODER/ DRIVER CHIP TO DRIVE LED DISPLAY

- 17. TRANSFER CHARACTERISTICS OF TTL AND CMOS NAND GATE

| L/1 1 100. 1_ | EXPT | NO: | 1_ |

|---------------|------|-----|----|

|---------------|------|-----|----|

DATE: \_\_/\_\_/\_\_

#### FAMILIARIZATION OF LOGIC GATES

**OBJECTIVE:**

To familiarize logic gates.

# HARDWARE REQUIRED:

| SLNo. | Components/Equipments | Specification | Quantity |  |

|-------|-----------------------|---------------|----------|--|

| 1.    | Digital Trainer Kit   |               | 1        |  |

| 2.    | IC                    | 7408          | 1        |  |

|       |                       | 7432          | 1        |  |

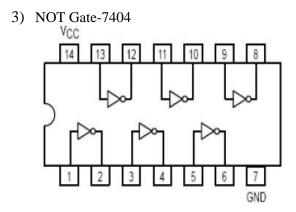

|       |                       | 7404          | 1        |  |

|       |                       | 7400          | 1        |  |

|       |                       | 7402          | 1        |  |

|       |                       | 7486          | 1        |  |

|       |                       | 7410          | 1        |  |

|       |                       | 7411          | 1        |  |

## **INTRODUCTION:**

A **logic gate** is an idealized or physical device implementing a Boolean function, that is, it performs a logical operation on one or more logic inputs and produces a single logic. There are seven basic logic gates: AND, OR, XOR, NOT, NAND, NOR, and XNOR.

The **AND gate** is so named because, if 0 is called "false" and 1 is called "true," the gate acts in the same way as the logical "and" operator. The output is "true" when both inputs are "true." Otherwise, the output is "false."

The **OR gate** gets its name from the fact that it behaves after the fashion of the logical inclusive "or." The output is "true" if either or both of the inputs are "true." If both inputs are "false," then the output is "false."

A **NOT gate** sometimes called a logical inverter to differentiate it from other types of electronic inverter devices, has only one input. It reverses the logic state

The **NAND gate** operates as an AND gate followed by a NOT gate. It acts in the manner of the logical operation "and" followed by negation. The output is "false" if both inputs are "true." Otherwise, the output is "true."

The **NOR gate** is a combination OR gate followed by an inverter. Its output is "true" if both inputs are "false." Otherwise, the output is "false."

The **XOR**(exclusive-OR) **gate** acts in the same way as the logical "either/or." The output is "true" if either, but not both, of the inputs are "true." The output is "false" if both inputs are "false" or if both inputs are "true." Another way of looking at this circuit is to observe that the output is 1 if the inputs are different, but 0 if the inputs are the same.

The **XNOR** (exclusive-NOR) **gate** is a combination XOR gate followed by an inverter. Its output is "true" if the inputs are the same, and "false" if the inputs are different

## **CIRCUIT DIAGRAM AND OBSERVATIONS:**

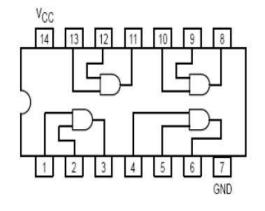

# 1) AND Gate-7408LS

# Truth table

| Α | В | O/P |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

2) OR Gate-7432LS

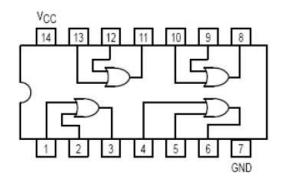

4) NAND Gate-7400LS

#### Truth table

| А | В | O/P |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

#### Truth table

| А | O/P |

|---|-----|

| 0 | 1   |

| 1 | 0   |

Truth table

A

B

O/P

0

0

1

0

1

1

1

0

1

1

0

1

5) NOR Gate-7402LS

Truth table

| А | В | O/P |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

6) EX-OR Gate-7486LS

Truth table

| А | В | O/P |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

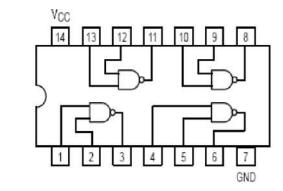

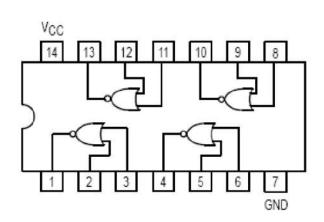

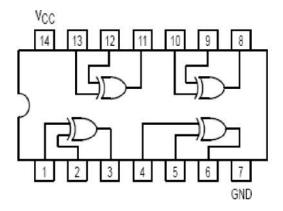

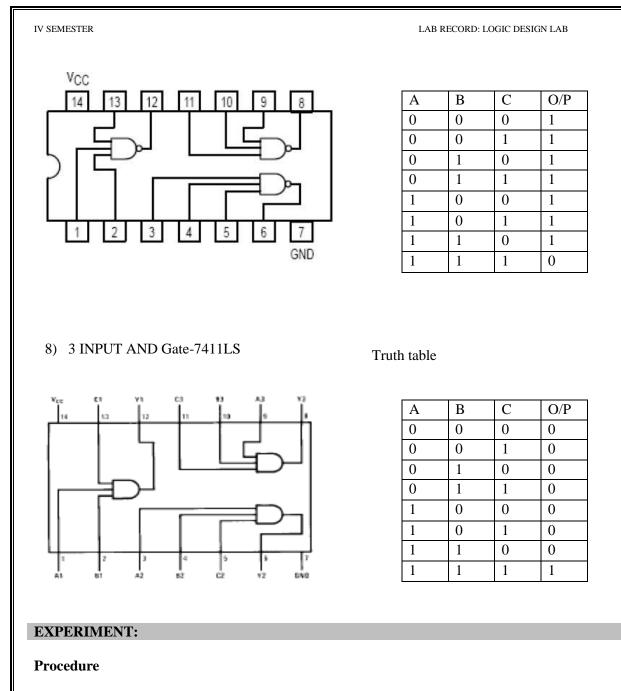

7) 3 INPUT NAND Gate-7410LS

- 1. Place the IC on IC Trainer Kit.

- 2. Connect  $V_{CC}$  and ground to respective pins of IC Trainer Kit.

- 3. Connect the inputs to the input switches provided in the IC Trainer Kit.

- 4. Connect the outputs to the switches of output LEDs

- 5. Apply various combinations of inputs according to the truth table and observe condition of LEDs

- 6. Disconnect output from the LEDs and note down the corresponding multimeter voltage readings for various combinations of inputs.

## CONCLUSION

Logic gates are familiarized. EXPT NO: 2

DATE: \_\_/\_\_/\_\_

# IMPLEMENTATION OF GIVEN BOOLEAN EXPRESSION USING LOGIC GATES IN SOP AND POS FORMS

#### **OBJECTIVE:**

To design and implement the given Boolean function using logic gates in sum of product and product of sum forms.

## HARDWARE REQUIRED:

| SLNo. | Components/Equipments | Specification | Quantity |

|-------|-----------------------|---------------|----------|

| 1.    | Digital Trainer Kit   |               | 1        |

| 2.    | IC                    | 7400          | 1        |

|       |                       | 7402          | 1        |

|       |                       | 7404          | 1        |

|       |                       | 7408LS        | 2        |

|       |                       | 7432          | 2        |

## **INTRODUCTION:**

Boolean algebra provides a concise way to express the operation of a logic circuit formed by a combination of logic gates so that the output can be determined for various combinations of input values.

All Boolean expressions regardless of their form can be converted into either of two standard forms: the sum of products form or the product of sum form. Standardization makes the evaluation, simplification and implementation of Boolean expressions much more systematic and easier.

# THE SUM OF PRODUCTS (SOP) FORM

When two or more product terms are summed by Boolean addition, the resulting expression is a sum of products (sop).

Example:

$$AB + ABC$$

$$A\overline{BC} + CD + A\overline{C}$$

$$AB + ABC + AC$$

Implementation of SOP Expression

Implementing SOP expression simply requires ORing the outputs of two or more AND gates. A product term is produced by an AND operation and the sum (addition) of two or more product terms is produced by an OR operation. Therefore, an SOP expression can be implemented by AND-OR logic in which the outputs of a number (equal to the number of product terms in the expression) of AND gates connect to the inputs of an OR gate. The output X of the OR gate equals the SOP expression. A SOP expression can always be implemented with one OR gate and two or more AND gates.

The standard POS form:

Any logic expression can be changed in to SOP form by applying Boolean algebra techniques.

The expression A (B+CD) can be converted to SOP form by applying the distributive law: Example:

$$A (B+CD) = AB + ACD$$

A standard SOP expression is one in which all the variables in the domain appear in each product term in the expression. Any nonstandard SOP expression can be converted to standard form using Boolean algebra.

#### THE PRODUCT-OF-SUM (POS) FORM

When two or more sum terms are multiplied, the resulting expression is a product-of-sums (POS). Examples:

$$(A + \overline{B} + C)(C + D)$$

$$(A + B)(\overline{A} + B + C)(C + \overline{D})$$

Implementation of POS expression:

Implementing a POS expression simply requires ANDing the outputs of two or more OR gates. A sum term is produced by an OR operation and the product of two or more sum term is produced by an AND operation. Therefore a POS expression can be implemented by a logic in which the outputs of number of OR gates connect to the input of an AND gate.

The standard POS form:

A standard POS expression is one in which all the variables in the domain appear in each sum term in the expression.

Example:

(A+B+C+D)(A+B+C+D)

Any nonstandard POS expression can be converted to the standard form using Boolean algebra.

#### CIRCUIT DIAGRAM AND OBSERVATIONS:

#### 1) Realization of SOP Boolean expression:

# Y = A'B'CD' + A'BCD' + ABCD' + AB'CD' + AB'C'D' + AB'C'D + AB'CD

|   | inpu | ts |   | O/F |

|---|------|----|---|-----|

| A | в    | C  | D | 0   |

| 0 | 0    | 0  | 0 | 0   |

| 0 | 0    | 0  | 1 | 0   |

| 0 | 0    | 1  | 0 | 1   |

| 0 | 0    | 1  | 1 | 0   |

| 0 | 1    | 0  | 0 | 0   |

| 0 | 1    | 0  | 1 | 0   |

| 0 | 1    | 1  | 0 | 1   |

| 0 | 1    | 1  | 1 | 0   |

| 1 | 0    | 0  | 0 | 1   |

| 1 | 0    | 0  | 1 | 1   |

| 1 | 0    | 1  | 0 | 1   |

| 1 | 0    | 1  | 1 | 1   |

| 1 | 1    | 0  | 0 | 0   |

| 1 | 1    | 0  | 1 | 0   |

| 1 | 1    | 1  | 0 | 1   |

| 1 | 1    | 1  | 1 | 0   |

Simplification using K-Map

| АВ | CD   | 00 | 01 | 11 | 10 |

|----|------|----|----|----|----|

|    | 00   | 0  | 0  | 0  | 1  |

|    | 01   | 0  | 0  | 0  | 1  |

|    | 11   | 0  | 0  | 0  | 1  |

|    | 10 [ | 1  | 1  | 1  | 1  |

Y = A.B' + C.D'

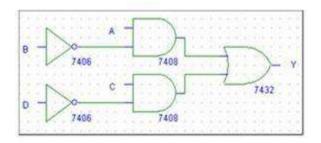

# Realization using basic Gates

# Realization using NAND Gates

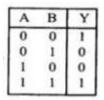

2) Realization of POS expression Y=(A+B)(A'+B')

# **Truthtable**

| Α | в | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

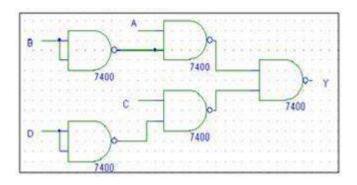

Realization using NAND Gates

Realization using NOR Gates

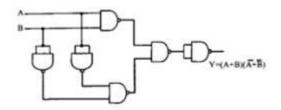

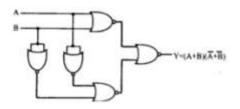

# 3) Realisation of SOP expression Y=AB+A'B'

# Truthtable

Realization using NAND Gates

Realization using NOR Gates

#### **EXPERIMENT:**

#### Procedure

- 1) Place the IC on IC Trainer Kit.

- 2) Connect  $V_{CC}$  and ground to respective pins of IC Trainer Kit .

- 3) Set up the circuit obtained from the expression

- 4) Connect the inputs to the input switches provided in the IC Trainer Kit.

- 5) Connect the outputs to the switches of output LEDs

- 6) Apply various combinations of inputs according to the truth table and observe condition of LEDs

# CONCLUSION

Implemented given boolean expression using logic gates in sop and pos forms.

## **REVIEW QUESTIONS:**

- 1)  $F=\sum m(0,1,2,3,4,5,6)$

- 2)  $F=\sum m(1,2,3,6,8,12,14,15)$

- 3)  $F=\prod M(0,3,5)$

- 4)  $F=\prod M(1,2,3,6,8,12,14,15)$

#### EXPT NO: 3

DATE: \_\_/\_\_/\_\_

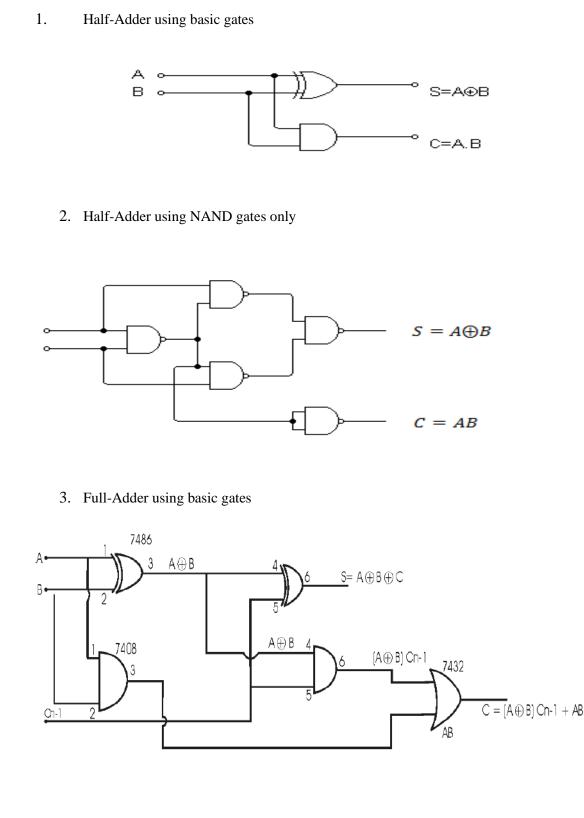

#### DESIGN AND IMPLEMENTATION OF ARITHMETIC CIRCUITS

#### **OBJECTIVE:**

To design and implement the Arithmetic Circuits

#### HARDWARE REQUIRED:

| SLNo. | Components/Equipments | Specification | Quantity |

|-------|-----------------------|---------------|----------|

| 1.    | Digital Trainer Kit   |               | 1        |

| 2.    | IC                    | 7400          | 3        |

|       |                       | 7408          | 1        |

|       |                       | 7486          | 1        |

|       |                       | 7410          | 1        |

|       |                       | 7432          | 1        |

#### **INTRODUCTION:**

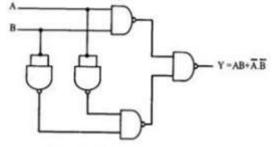

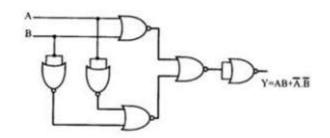

#### Half adder

With the help of half adder, we can design circuits that are capable of performing simple addition with the help of logic gates. The truth table of half adder is shown below. Sum, s is the normal output and carry, c is the carry-out.

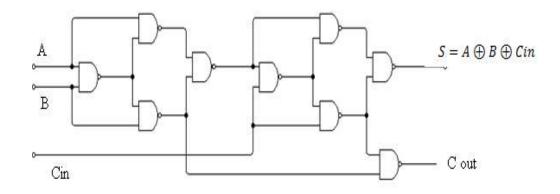

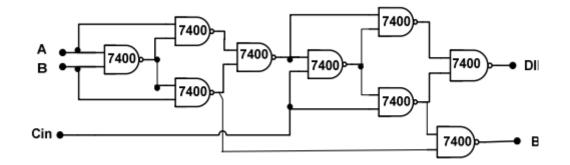

#### Full adder

This type of adder is a little more difficult to implement than a half-adder. The main difference between a half-adder and a full-adder is that the full-adder has three inputs and two outputs. The first two inputs are A and B and the third input is an input carry designated as CIN. When a full adder logic is designed we will be able to string eight of them together to create a byte-wide adder and cascade the carry bit from one adder to the next. The output carry is designated as C and the normal output is designated as S.

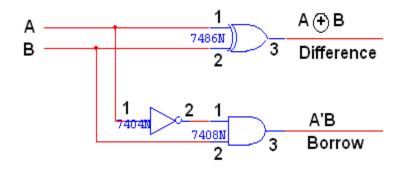

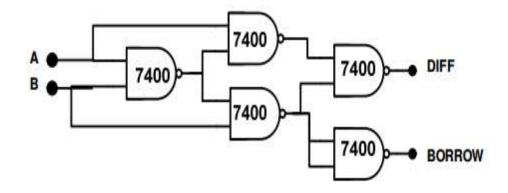

#### Half subtractor:

The half subtractor is constructed using X-OR and AND Gate. The half subtractor has two input and two outputs. The outputs are difference and borrow. The difference can be applied using X-OR Gate, borrow output can be implemented using an AND Gate and an inverter.

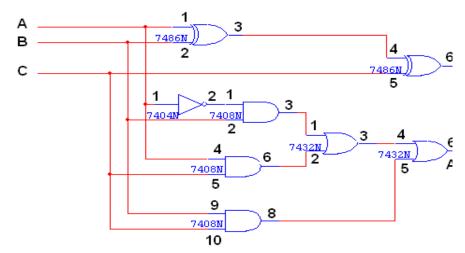

#### **Full subtractor:**

The full subtractor is a combination of X-OR, AND, OR, NOT Gates. In a full subtractor the logic circuit should have three inputs and two outputs. The two half subtractor put together gives a full

subtractor .The first half subtractor will be C and A B. The output will be difference output of full subtractor. The expression AB assembles the borrow output of the half subtractor and the second term is the inverted difference output of first X-OR.

# **CIRCUIT DIAGRAM:**

#### IV SEMESTER

4. Full-Adder using NAND gates only

5. Half-subtractor using basic gates

6. Half-subtractor using NAND gates only

#### IV SEMESTER

7. Full-subtractor using Basic gates.

8. Full-subtractor using NAND gates only

# **DESIGN:**

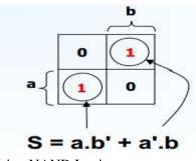

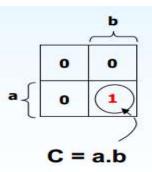

1) Half adder

| Inputs |   | Outputs |   |

|--------|---|---------|---|

| A      | В | S       | С |

| 0      | 0 | 0       | 0 |

| 0      | 1 | 1       | 0 |

| 1      | 0 | 1       | 0 |

| 1      | 1 | 0       | 1 |

#### Using basic gates

Using NAND Logic

$$S = A\overline{B} + \overline{A}B = A\overline{B} + A\overline{A} + \overline{A}B + B\overline{B}$$

$$= A(\overline{A} + \overline{B}) + B(\overline{A} + \overline{B})$$

$$= A \cdot \overline{AB} + B \cdot \overline{AB}$$

$$= \overline{\overline{A \cdot AB} \cdot \overline{B \cdot AB}}$$

$$C = AB = \overline{AB}$$

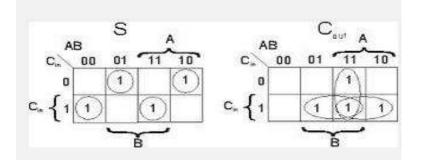

2) Full adder

| Inputs |                   |   | Sum | Carry |  |

|--------|-------------------|---|-----|-------|--|

| A      | B C <sub>in</sub> |   | S   | Cout  |  |

| 0      | 0                 | 0 | 0   | 0     |  |

| 0      | 0                 | 1 | 1   | 0     |  |

| 0      | 1                 | 0 | 1   | 0     |  |

| 0      | 1                 | 1 | 0   | 1     |  |

| 1      | 0                 | 0 | 1   | 0     |  |

| 1      | 0                 | 1 | 0   | 1     |  |

| 1      | 1                 | 0 | 0   | 1     |  |

| 1      | 1                 | 1 | 1   | 1     |  |

Using basic gates

$$S = \overline{ABC}_{in} + \overline{AB}\overline{C}_{in} + \overline{ABC}_{in} + ABC_{in}$$

=  $(A\overline{B} + \overline{AB})\overline{C}_{in} + (AB + \overline{AB})C_{in} = (A \oplus B)\overline{C}_{in} + (\overline{A \oplus B})C_{in} = A \oplus B \oplus C_{in}$

$$C_{out} = \overline{ABC}_{in} + A\overline{BC}_{in} + AB\overline{C}_{in} + ABC_{in} = AB + (A \oplus B)C_{in} = AB + AC_{in} + BC_{in}$$

Using NAND Logic

$$S = A \oplus B \oplus C_{in} = \overline{(A \oplus B) \cdot \overline{(A \oplus B)C_{in}}} \cdot \overline{C_{in} \cdot \overline{(A \oplus B)C_{in}}}$$

$$C_{out} = C_{in}(A \oplus B) + AB = \overline{C_{in}(A \oplus B)} \cdot \overline{AB}$$

#### 3)Half-Subtractor

# Truth table:

| Α | В | BORROW | DIFFERENCE |

|---|---|--------|------------|

| 0 | 0 | 0      | 0          |

| 0 | 1 | 1      | 1          |

| 1 | 0 | 0      | 1          |

| 1 | 1 | 0      | 0          |

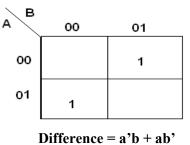

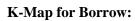

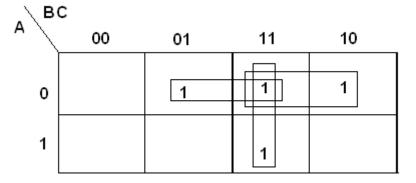

# K-Map for DIFFERENCE:

K-map for borrow:

Borrow = a'b

USING NAND ONLY:

Difference D =  $\stackrel{A \oplus B}{\longrightarrow} = \stackrel{\overline{A.\overline{AB}}.\overline{B.\overline{AB}}}{=}$ Borrow B=  $\stackrel{A\overline{B}}{=} = \stackrel{B(\overline{A}+\overline{B})=B(\overline{AB})=\overline{B.\overline{AB}}}{=}$  IV SEMESTER

4)Full-Subtractor

| Α | B | С | BORROW | DIFFERENCE |

|---|---|---|--------|------------|

|   |   |   |        |            |

| 0 | 0 | 0 | 0      | 0          |

| 0 | 0 | 1 | 1      | 1          |

| 0 | 1 | 0 | 1      | 1          |

| 0 | 1 | 1 | 1      | 0          |

| 1 | 0 | 0 | 0      | 1          |

| 1 | 0 | 1 | 0      | 0          |

| 1 | 1 | 0 | 0      | 0          |

| 1 | 1 | 1 | 1      | 1          |

|   |   |   |        |            |

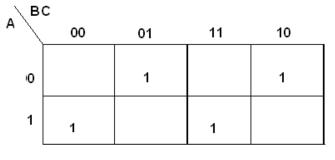

# K-Map for Difference:

**Difference = A'B'C + A'BC' + AB'C' + ABC**

Borrow = A'B + BC + A'C

USING NAND ONLY:

Difference  $D = ^{A} \oplus B \oplus C = \overline{A \oplus B \oplus C} = \overline{(A \oplus B)(A \oplus B)C c(\overline{A \oplus B})C c(\overline{A \oplus B})C}$ Borrow  $B = \overline{AB.C(A \oplus B)} = \overline{AB.C(A \oplus B)}$  IV SEMESTER

## **EXPERIMENT:**

## Procedure

- 1) Place the IC on IC Trainer Kit.

- 2) Connect  $V_{CC}$  and ground to respective pins of IC Trainer Kit.

- 3) Connect the inputs to the input switches provided in the IC Trainer Kit.

- 4) Connect the outputs to the switches of output LEDs

- 5) Apply various combinations of inputs according to the truth table and observe condition of LEDs

#### **OBSERVATIONS:**

#### Truthtable

# Half-Adder

| A | В | S | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

## **Full Adder**

|   | В | CIN | s | COUT |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

# Half –Subtractor

| Α | В | Borrow | Difference |

|---|---|--------|------------|

| 0 | 0 | 0      | 0          |

| U | 0 | 0      | 0          |

| 0 |   | 1      |            |

| 1 | 0 | U      |            |

| 1 | 1 | 0      | 0          |

|   |   |        |            |

|   |   |        |            |

# **Full-Subtractor**

| Α | В | С | Borrow | Difference |

|---|---|---|--------|------------|

|   |   |   |        |            |

| 0 | 0 | 0 | 0      | 0          |

| 0 | 0 | 1 | 1      | 1          |

| 0 | 1 | 0 | 1      | 1          |

| 0 | 1 | 1 | 1      | 0          |

| 1 | 0 | 0 | 0      | 1          |

| 1 | 0 | 1 | 0      | 0          |

| 1 | 1 | 0 | 0      | 0          |

| 1 | 1 | 1 | 1      | 1          |

|   |   |   |        |            |

# CONCLUSION

Arithmetic circuits are designed and implemented

EXPT NO:4

DATE: \_\_/\_\_/\_\_

## 4 BIT ADDER/SUBTRACTOR AND BCD ADDER USING 7483

#### **OBJECTIVE:**

To design a 4 bit adder/subtractor and BCD Adder using 7483.

## HARDWARE REQUIRED:

| SLNo. | Components/Equipments | Specification | Quantity |

|-------|-----------------------|---------------|----------|

| 1.    | Digital Trainer Kit   |               | 1        |

| 2.    | IC                    | 7483          | 2        |

|       |                       | 7408          | 1        |

|       |                       | 7432          | 1        |

|       |                       | 7486          | 1        |

#### **INTRODUCTION:**

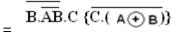

#### 4 bit binary adder/subtractor:

A binary adder is a digital circuit that produces the arithmetic sum of two binary numbers. It can be constructed with full adders connected in cascade, with the output carry from each full adder connected to the input carry of next full adder in chain. The augends bits of 'A' and the addend bits of 'B' are designated by subscript numbers from right to left, with subscript 0 denoting the least significant bits. The carries are connected in chain through the full adder. The input carry to the adder is  $C_0$  and it ripples through the full adder to the output carry  $C_4$ .

The circuit for subtracting A-B consists of an adder with inverters, placed between each data input 'B' and the corresponding input of full adder. The input carry  $C_0$  must be equal to 1 when performing subtraction.

The addition and subtraction operation can be combined into one circuit with one common binary adder. The mode input M controls the operation. When M=0, the circuit is adder circuit. When M=1, it becomes subtractor.

#### 4 bit BCD adder:

Consider the arithmetic addition of two decimal digits in BCD, together with an input carry from a previous stage. Since each input digit does not exceed 9, the output sum cannot be greater than 19, the 1 in the sum being an input carry. The output of two decimal digits must be represented in BCD and should appear in the form listed in the columns.

ABCD adder that adds 2 BCD digits and produce a sum digit in BCD. The 2 decimal digits, together with the input carry, are first added in the top 4 bit adder to produce the binary sum.

#### Pin diagram for IC 7483:

| 1 | _ A4  |    | B4 — 16  |

|---|-------|----|----------|

| 2 | – S3  | I. | S4 — 15  |

| 3 | _ A3  | С  | C4 — 14  |

| 4 | _ вз  | 7  | C1 — 13  |

| 5 | _ vcc | 4  | GND — 12 |

| 6 | _ S2  | 8  | B1 — 11  |

| 7 | — В2  | 3  | A1 — 10  |

| 8 | — A2  |    | S1 — 9   |

|   |       |    |          |

#### **CIRCUIT DIAGRAM AND OBSERVATIONS:**

## **4-BIT BINARY ADDER/SUBTRACTOR**

# **BCD ADDER:**

| Input Data A Input I |    | Data | B  |               | А          | dditi | on |      | Subtraction |            |      |           |    |    |    |      |   |

|----------------------|----|------|----|---------------|------------|-------|----|------|-------------|------------|------|-----------|----|----|----|------|---|

| A4                   | A3 | A2   | A1 | <b>B4</b>     | <b>B</b> 3 | B2    | B1 | С    | <b>S4</b>   | <b>S</b> 3 | S2   | <b>S1</b> | B  | D4 | D3 | D2   | D |

| 1                    | 0  | 0    | 0  | 0             | 0          | 1     | 0  | 0    | 1           | 0          | 1    | 0         | 1  | 0  | 1  | 1    | 0 |

| 1                    | 0  | 0    | 0  | 1             | 0          | 0     | 0  | 1    | 0           | 0          | 0    | 0         | 1  | 0  | 0  | 0    | 0 |

| 0                    | 0  | 1    | 0  | 1             | 0          | 0     | 0  | 0    | 1           | 0          | 1    | 0         | 0  | 1  | 0  | 1    | 0 |

| 0                    | 0  | 0    | 1  | 0             | 1          | 1     | 1  | 0    | 1           | 0          | 0    | 0         | 0  | 1  | 0  | 1    | 0 |

| 1                    | 0  | 1    | 0  | 1             | 0          | 1     | 1  | 1    | 0           | 0          | 1    | 0         | 0  | 1  | 1  | 1    | 1 |

| 1                    | 1  | 1    | 0  | 1             | 1          | 1     | 1  | 1    | 1           | 0          | 1    | 0         | 0  | 1  | 1  | 1    | 1 |

| 1                    | 0  | 1    | 0  | 1             | 1          | 0     | 1  | 1    | 0           | 1          | 1    | 1         | 0  | 1  | 1  | 0    | 1 |

|                      |    | 743  | 2N |               | $\Box$     |       |    | 7408 | N           | \$         | 54 5 | S3 :      | S2 | S1 | _  |      |   |

|                      |    |      |    |               | 7432N      |       |    | 7408 | -           |            |      |           | -  |    |    |      |   |

|                      |    |      |    |               | 0          | _     | A  | 4 A  | 3 A         | 2 A        | 1 E  | 84 1      | B3 | B2 | B1 |      |   |

|                      |    |      |    |               |            |       | 1  | 3    | 8           | 10         | 16   | 4         | 7  | 11 | _  | CE = | 0 |

|                      |    |      |    | arry<br>gnore | d          | -     |    | l,   | C 7         | 74         | 83   |           |    |    |    | vcc  |   |

|                      |    |      |    |               |            |       |    |      |             |            | 15   | 2         | 6  | 9  | -  | GND  |   |

|                      |    |      |    |               |            |       |    |      |             |            | -10  | 4         | 0  |    |    |      |   |

K map:

$$Y = C4 + S4 (S3 + S2)$$

Truth table:

|           | BCD       | SUM |           | CARRY |

|-----------|-----------|-----|-----------|-------|

| <b>S4</b> | <b>S3</b> | S2  | <b>S1</b> | С     |

| 0         | 0         | 0   | 0         | 0     |

| 0         | 0         | 0   | 1         | 0     |

| 0         | 0         | 1   | 0         | 0     |

| 0         | 0         | 1   | 1         | 0     |

| 0         | 1         | 0   | 0         | 0     |

| 0         | 1         | 0   | 1         | 0     |

| 0         | 1         | 1   | 0         | 0     |

| 0         | 1         | 1   | 1         | 0     |

| 1         | 0         | 0   | 0         | 0     |

| 1         | 0         | 0   | 1         | 0     |

| 1         | 0         | 1   | 0         | 1     |

| 1         | 0         | 1   | 1         | 1     |

| 1         | 1         | 0   | 0         | 1     |

| 1         | 1         | 0   | 1         | 1     |

| 1         | 1         | 1   | 0         | 1     |

| 1         | 1         | 1   | 1         | 1     |

## **EXPERIMENT:**

#### Procedure

- 1) Connections were given as per circuit diagram.

- 2) Logical inputs were given as per truth table

- 3) Observe the logical output and verify with the truth tables.

# CONCLUSION

The 4 bit adder/subtractor and BCD adder are designed and implemented using 7483.

#### EXPT NO:5

DATE: \_\_/\_\_/\_\_

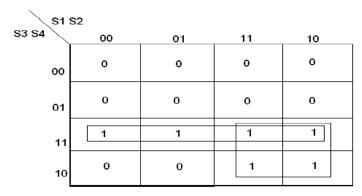

#### 2/3 BIT BINARY COMPARATOR

#### **OBJECTIVE:**

To design a 2/3 bit binary comparator

## HARDWARE REQUIRED:

| SLNo. | Components/Equipments | Specification | Quantity |

|-------|-----------------------|---------------|----------|

| 1.    | Digital Trainer Kit   |               | 1        |

| 2.    | IC                    | IC 7408       | 2        |

|       |                       | IC 7486       | 1        |

|       |                       | IC 7432       | 1        |

|       |                       | IC 7404       | 1        |

|       |                       | IC 7485       | 2        |

#### **INTRODUCTION:**

The comparison of two numbers is an operator that determine one number is greater than, less than (or) equal to the other number. A magnitude comparator is a combinational circuit that compares two numbers A and B and determine their relative magnitude. The outcome of the comparator is specified by three binary variables that indicate whether A>B, A=B (or) A<B.

$A=A_3\ A_2\ A_1\ A_0$

#### $B=B_3\ B_2\ B_1\ B_0$

The equality of the two numbers and B is displayed in a combinational circuit designated by the symbol (A=B).

This indicates A greater than B, then inspect the relative magnitude of pairs of significant digits starting from most significant position. A is 0 and that of B is 0.

We have A<B, the sequential comparison can be expanded as

$$A > B = A3B_3^1 + X_3A_2B_2^1 + X_3X_2A_1B_1^1 + X_3X_2X_1A_0B_0^1$$

$$A < B = A_3^{1}B_3 + X_3A_2^{1}B_2 + X_3X2A_1^{1}B_1 + X_3X_2X_1A_0^{1}B_0$$

The same circuit can be used to compare the relative magnitude of two BCD digits. Where, A = B is expanded as,

IV SEMESTER

LAB RECORD: LOGIC DESIGN LAB

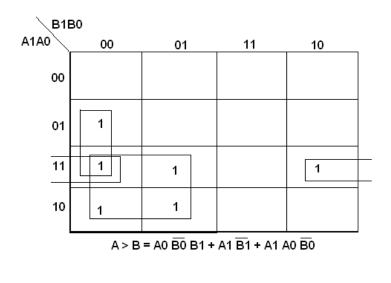

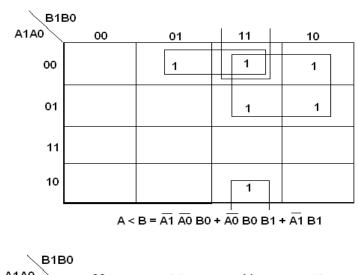

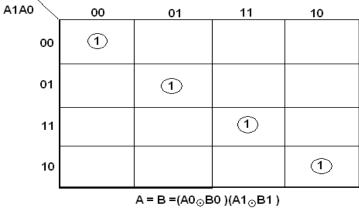

# CIRCUIT DIAGRAM AND OBSERVATIONS:

# **2 BIT MAGNITUDE COMPARATOR**

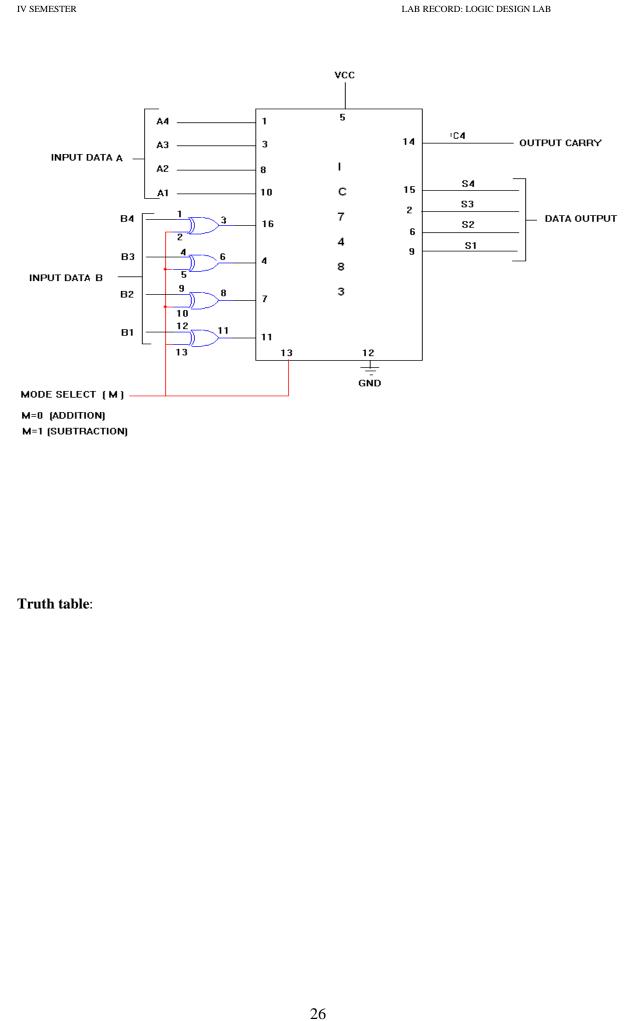

K MAP

IV SEMESTER

# TRUTH TABLE

| A1 | A0 | <b>B1</b> | <b>B0</b> | A > B | $\mathbf{A} = \mathbf{B}$ | A < B |

|----|----|-----------|-----------|-------|---------------------------|-------|

| 0  | 0  | 0         | 0         | 0     | 1                         | 0     |

| 0  | 0  | 0         | 1         | 0     | 0                         | 1     |

| 0  | 0  | 1         | 0         | 0     | 0                         | 1     |

| 0  | 0  | 1         | 1         | 0     | 0                         | 1     |

| 0  | 1  | 0         | 0         | 1     | 0                         | 0     |

| 0  | 1  | 0         | 1         | 0     | 1                         | 0     |

| 0  | 1  | 1         | 0         | 0     | 0                         | 1     |

| 0  | 1  | 1         | 1         | 0     | 0                         | 1     |

| 1  | 0  | 0         | 0         | 1     | 0                         | 0     |

| 1  | 0  | 0         | 1         | 1     | 0                         | 0     |

| 1  | 0  | 1         | 0         | 0     | 1                         | 0     |

| 1  | 0  | 1         | 1         | 0     | 0                         | 1     |

| 1  | 1  | 0         | 0         | 1     | 0                         | 0     |

| 1  | 1  | 0         | 1         | 1     | 0                         | 0     |

| 1  | 1  | 1         | 0         | 1     | 0                         | 0     |

| 1  | 1  | 1         | 1         | 0     | 1                         | 0     |

# **EXPERIMENT:**

#### Procedure

- 1) Place the IC on IC Trainer Kit.

- 2) Connect  $V_{CC}$  and ground to respective pins of IC Trainer Kit.

- 3) Test all the components and IC packages using multimeter or digital IC tester. Set up the circuits and verify their truth table.

# CONCLUSION

Designed and implemented a 2/3 bit binary comparator.

#### EXPT NO:6

DATE: \_\_/\_\_/\_\_\_

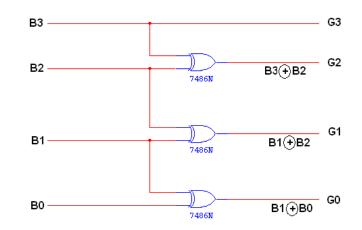

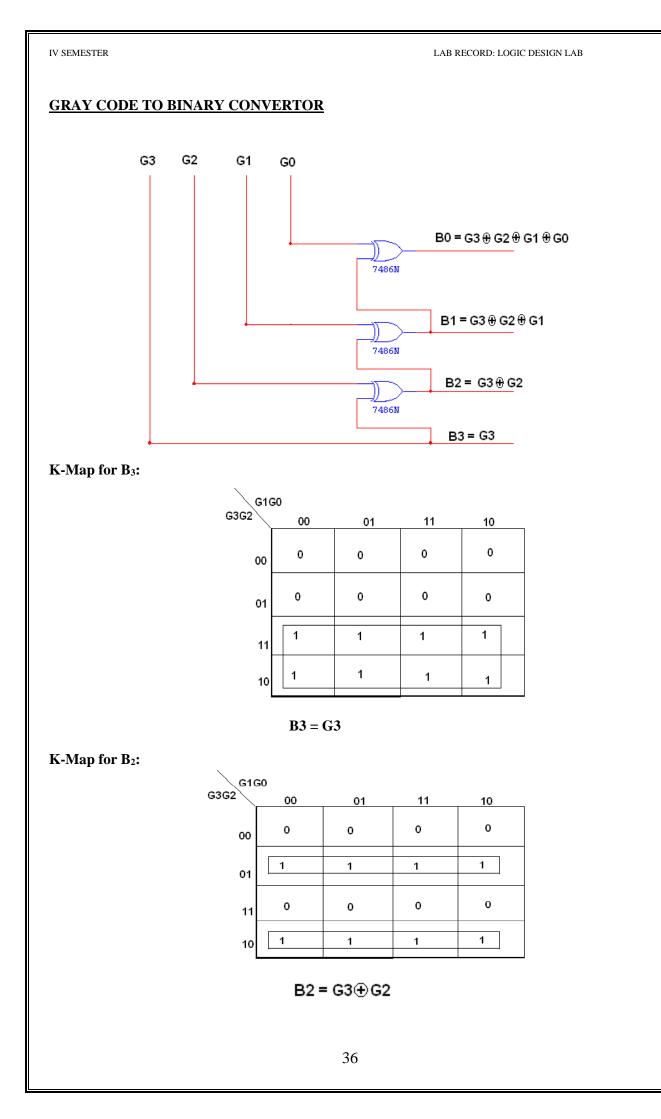

# BINARY TO GRAY AND GRAY TO BINARY CONVERTERS

#### **OBJECTIVE:**

To design the following circuits (a)binary to gray converter (b)gray to binary converter

#### HARDWARE REQUIRED:

| SLNo. | Components/Equipments | Specification | Quantity |

|-------|-----------------------|---------------|----------|

| 1.    | Digital Trainer Kit   |               | 1        |

| 2.    | IC                    | IC 7486       | 1        |

|       |                       | IC 7408       | 1        |

|       |                       | IC 7432       | 1        |

|       |                       | IC 7404       | 1        |

#### **INTRODUCTION:**

The availability of large variety of codes for the same discrete elements of information results in the use of different codes by different systems. A conversion circuit must be inserted between the two systems if each uses different codes for same information. Thus, code converter is a circuit that makes the two systems compatible even though each uses different binary code.

The bit combination assigned to binary code to gray code. Since each code uses four bits to represent a decimal digit. There are four inputs and four outputs. Gray code is a non-weighted code.

The input variable are designated as B3, B2, B1, B0 and the output variables are designated as C3, C2, C1, Co. from the truth table, combinational circuit is designed. The Boolean functions are obtained from K-Map for each output variable.

A code converter is a circuit that makes the two systems compatible even though each uses a different binary code. To convert from binary code to Excess-3 code, the input lines must supply the bit combination of elements as specified by code and the output lines generate the corresponding bit combination of code. Each one of the four maps represents one of the four outputs of the circuit as a function of the four input variables.

A two-level logic diagram may be obtained directly from the Boolean expressions derived by the maps. These are various other possibilities for a logic diagram that implements this circuit. Now the OR gate whose output is C+D has been used to implement partially each of three outputs.

## CIRCUIT DIAGRAM AND OBSERVATIONS:

# BINARY TO GRAY CODE CONVERTOR

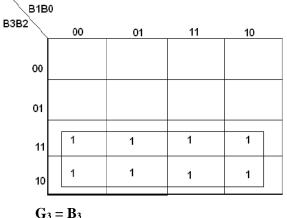

# K-Map for G<sub>3</sub>:

$$\mathbf{G}_3 = \mathbf{B}_3$$

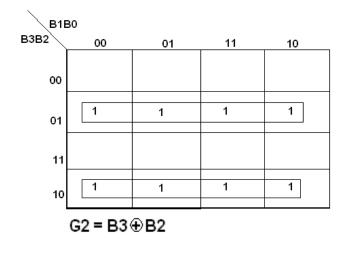

# K-Map for G<sub>2</sub>:

IV SEMESTER

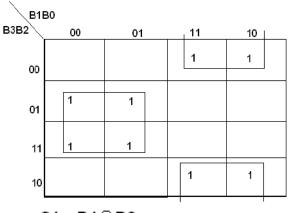

# K-Map for G<sub>1</sub>:

K-Map for G<sub>0</sub>:

G0 = B1⊕B0

# **TRUTH TABLE:**

|    | Binary | input |           | Gray code output |    |    |    |  |

|----|--------|-------|-----------|------------------|----|----|----|--|

| B3 | B2     | B1    | <b>B0</b> | G3               | G2 | G1 | GO |  |

| 0  | 0      | 0     | 0         | 0                | 0  | 0  | 0  |  |

| 0  | 0      | 0     | 1         | 0                | 0  | 0  | 1  |  |

| 0  | 0      | 1     | 0         | 0                | 0  | 1  | 1  |  |

| 0  | 0      | 1     | 1         | 0                | 0  | 1  | 0  |  |

| 0  | 1      | 0     | 0         | 0                | 1  | 1  | 0  |  |

| 0  | 1      | 0     | 1         | 0                | 1  | 1  | 1  |  |

| 0  | 1      | 1     | 0         | 0                | 1  | 0  | 1  |  |

| 0  | 1      | 1     | 1         | 0                | 1  | 0  | 0  |  |

| 1  | 0      | 0     | 0         | 1                | 1  | 0  | 0  |  |

| 1  | 0      | 0     | 1         | 1                | 1  | 0  | 1  |  |

| 1  | 0      | 1     | 0         | 1                | 1  | 1  | 1  |  |

| 1  | 0      | 1     | 1         | 1                | 1  | 1  | 0  |  |

| 1  | 1      | 0     | 0         | 1                | 0  | 1  | 0  |  |

| 1  | 1      | 0     | 1         | 1                | 0  | 1  | 1  |  |

| 1  | 1      | 1     | 0         | 1                | 0  | Ō  | 1  |  |

| 1  | 1      | 1     | 1         | 1                | 0  | 0  | 0  |  |

|    |        |       |           |                  |    |    |    |  |

LAB RECORD: LOGIC DESIGN LAB

IV SEMESTER

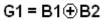

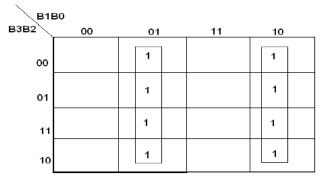

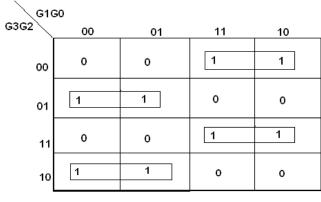

# K-Map for B<sub>1</sub>:

# K-Map for B<sub>0</sub>:

| G10  | 30 |    |    |    |

|------|----|----|----|----|

| G3G2 | 00 | 01 | 11 | 10 |

| 00   | 0  | 1  | 0  | 1  |

| 01   | 1  | o  | 1  | 0  |

| 11   | 0  | 1  | 0  | 1  |

| 10   | 1  | 0  | 1  | 0  |

Ι

B0 = G3⊕G2⊕G1⊕G0

1

## **TRUTH TABLE:**

L

**Gray Code**

**Binary Code**

| G3 | G2 | G1 | GO | B3 | B2 | B1 | BO |

|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  |

| 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  |

| 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  |

| 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  |

| 0  | 1  | 1  | 1  | 0  | 1  | 0  | 1  |

| 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  |

| 0  | 1  | 0  | 0  | 0  | 1  | 1  | 1  |

| 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  |

| 1  | 1  | 0  | 1  | 1  | 0  | 0  | 1  |

| 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  |

| 1  | 1  | 1  | 0  | 1  | 0  | 1  | 1  |

| 1  | 0  | 1  | 0  | 1  | 1  | 0  | 0  |

| 1  | 0  | 1  | 1  | 1  | 1  | 0  | 1  |

| 1  | 0  | 0  | 1  | 1  | 1  | 1  | 0  |

| 1  | 0  | 0  | 0  | 1  | 1  | 1  | 1  |

|    |    |    |    |    |    |    |    |

### **EXPERIMENT:**

### Procedure

- 1) Connections were given as per circuit diagram.

- 2) Logical inputs were given as per truth table

- 3) Observe the logical output and verify with the truth tables

### CONCLUSION

Designed and implemented a binary to gray and gray to binary converter.

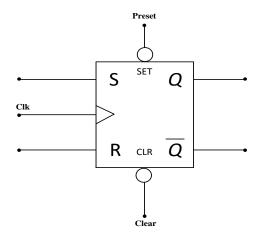

. EXPT NO:7

DATE: \_\_/\_\_/\_\_

### **FLIP FLOPS**

### **OBJECTIVE:**

To implement various flip flops using NAND gates and to familiarize the ICs 7474 and 7476

## HARDWARE REQUIRED:

| SLNo. | Components/Equipments | Specification | Quantity |

|-------|-----------------------|---------------|----------|

| 1.    | Digital Trainer Kit   |               | 1        |

| 2.    | IC                    | 7400          | 2        |

|       |                       | 7410          | 2        |

|       |                       | 7404          | 1        |

|       |                       | 7474          | 1        |

|       |                       | 7476          | 1        |

### **INTRODUCTION:**

Flip flops are the basic building blocks in any memory system, since its output will remain in its state until it is forced to change it by some means.

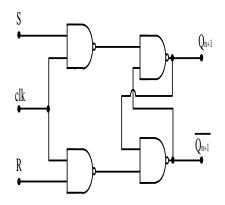

### **CLOCKED SR FLIP FLOP**

S and R stands for set and reset. There are 4 input combinations possible. But S=R=1 is forbidden, since the output will be invalid. When the flip flop is switched on, its output state will be uncertain. When an initial state is to be assigned, two separate inputs called preset and clear are used. They are active low inputs.

### **JK FLIP FLOPS**

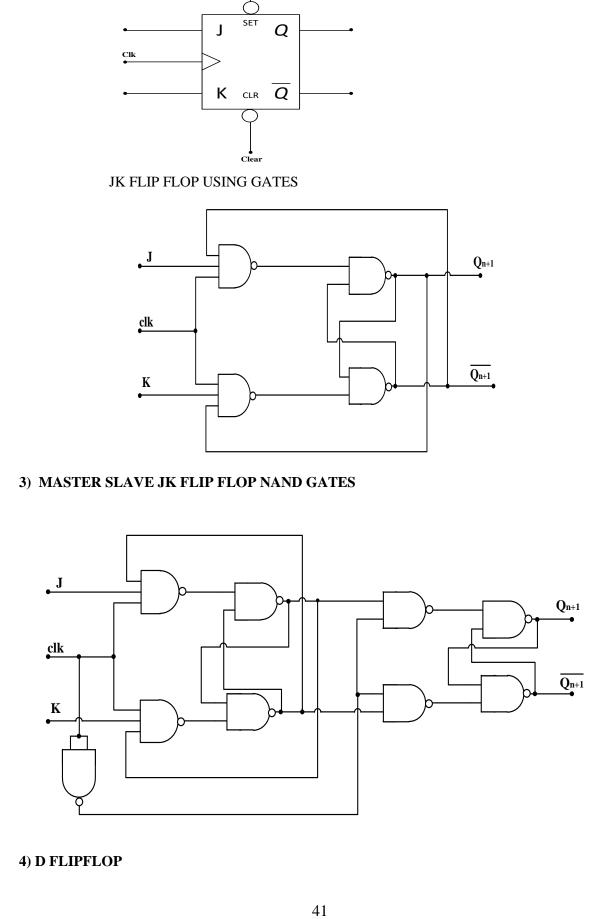

The invalid output state of S-R flip flop, when S=R=1 is avoided by converting it into a J-K flip flop.

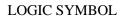

### MASTER SLAVE JK FLIP FLOPS

The race around condition of JK flip flop is rectified in Master Slave JK flip flop. Racing is the toggling of the output more than once during a positive clock edge. Master Slave JK flip flop is created by cascading two JK flip flops. The clock fed to the first stage (master) is inverted and fed to the second stage (slave). This ensures that the slave follows the master eliminates the chance of racing.

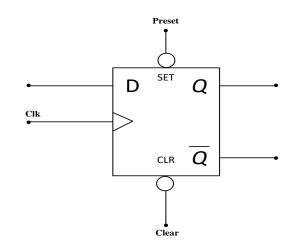

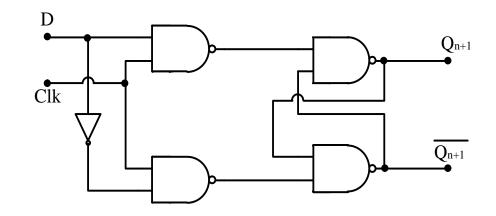

#### **D FLIP FLOP**

It has only on input referred to as D input or data input. The input data is transferred to the output after a clock pulse applied. D flip flop can be derived JK flip flops by using J inputs as D input and J is inverted and fed to K input.

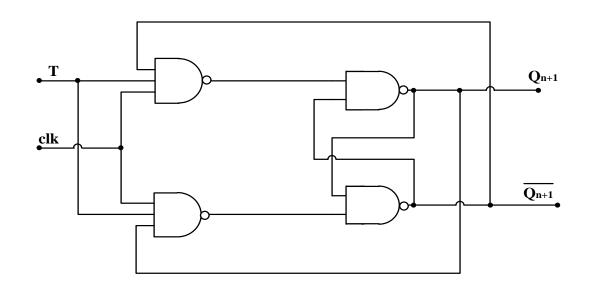

#### **T FLIP FLOP**

T stands for toggle. The output toggles when a clock pulse is applied. That is the output of the flip flop changes state for an input pulse. T flip flop can be derived from JK flip flop by shorting J and K inputs.

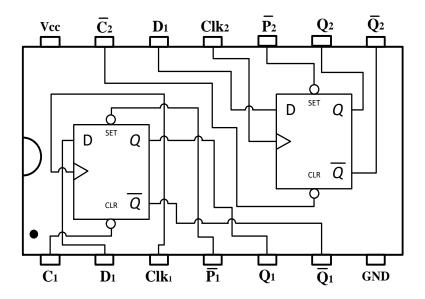

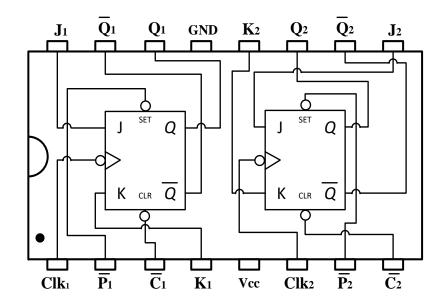

#### **FLIP FLOP ICS**

IC 7476 is dual negative edge triggered MS JK flip flop with preset and clear facility. It has a 16 pin DIP chip. IC 7473 is a dual negative edge triggering Master Slave JK flip flop with clear in 14 pin DIP. It does not have preset input. IC 7474 is positive edge triggered dual D flip flop with preset and clear in 14 pin DIP.

#### **CIRCUIT DIAGRAM :**

### 1) SR FLIPFLOP

# LOGIC SYMBOL

# SR FLIP FLOP USING GATES

2) JK FLIP FLOP

LOGIC SYMBOL

D FLIP FLOP USING GATES

LOGIC SYMBOL

T FLIP FLOP USING GATES

LAB RECORD: LOGIC DESIGN LAB

### **FLIP FLOP ICS**

# D FLIP FLOP IC- 7474

LAB RECORD: LOGIC DESIGN LAB

### **JK FLIPFLOP IC-7476**

### **EXPERIMENT:**

### Procedure

- 1) Place the IC on IC Trainer Kit.

- 2) Connect  $V_{CC}$  and ground to respective pins of IC Trainer Kit.

- 3) Test all the components and IC packages using multimeter or digital IC tester. Set up the flip flops using gates and verify their truth table.

- 4) Verify the truth tables of 7474,7476

### **OBSERVATIONS:**

### Truthtable

### 1) SR flipflop

| Inj | puts |                         |

|-----|------|-------------------------|

| S   | R    | <b>Q</b> <sub>n+1</sub> |

| 0   | 0    | Qn                      |

| 0   | 1    | 0                       |

| 1   | 0    | 1                       |

| 1   | 1    | ?                       |

### 2) JK flipflop

|   | Inputs |   | Out | puts |           |

|---|--------|---|-----|------|-----------|

| J | K      | С | Q   | Q'   | Comments  |

| 0 | 0      | Ŷ | Q   | Q'   | No change |

| 0 | 1      | 1 | 0   | 1    | RESET     |

| 1 | 0      | ↑ | 1   | 0    | SET       |

| 1 | 1      | 1 | Q'  | Q    | Toggle    |

# 3) Master slave JK flip-flop

| J | K | Q (t+                | 1)               |

|---|---|----------------------|------------------|

| 0 | 0 |                      | unchanged        |

| 0 | 1 | 0                    | reset            |

| 1 | 0 | 1                    | set              |

| 1 | 1 | $\overline{Q}_{(t)}$ | output inversion |

# 4) D flip flop

| Input          | Output           |

|----------------|------------------|

| D <sub>n</sub> | Q <sub>n+1</sub> |

| 0              | 0                |

| 1              | 1                |

# 5) T flip flop

| Т | Q  | Q |

|---|----|---|

| 0 | Q. | ã |

| 1 | ā  | Q |

| 0 | ā  | Q |

| 1 | Q  | ā |

# CONCLUSION

The flip-flops are implemented using NAND gates and outputs are verified EXPT NO: 8

DATE: \_\_/\_\_/\_\_

LAB RECORD: LOGIC DESIGN LAB

### **ASYNCHRONOUS COUNTERS**

### **OBJECTIVE:**

To realize the following asynchronous counters

(a) 4-bit up conter $\setminus$

(b) 4 bit down counter

- (c) Mod-10 counters

- (d) 3 bit up/down counter

#### HARDWARE REQUIRED:

| SLNo. | Components/Equipments | Specification | Quantity |

|-------|-----------------------|---------------|----------|

| 1.    | Digital Trainer Kit   |               | 1        |

| 2.    | IC                    | 7476,         | 1        |

|       |                       | 7400          | 1        |

|       |                       | 7473          | 1        |

|       |                       | 7486          | 1        |

#### **INTRODUCTION:**

#### Asynchronous counter

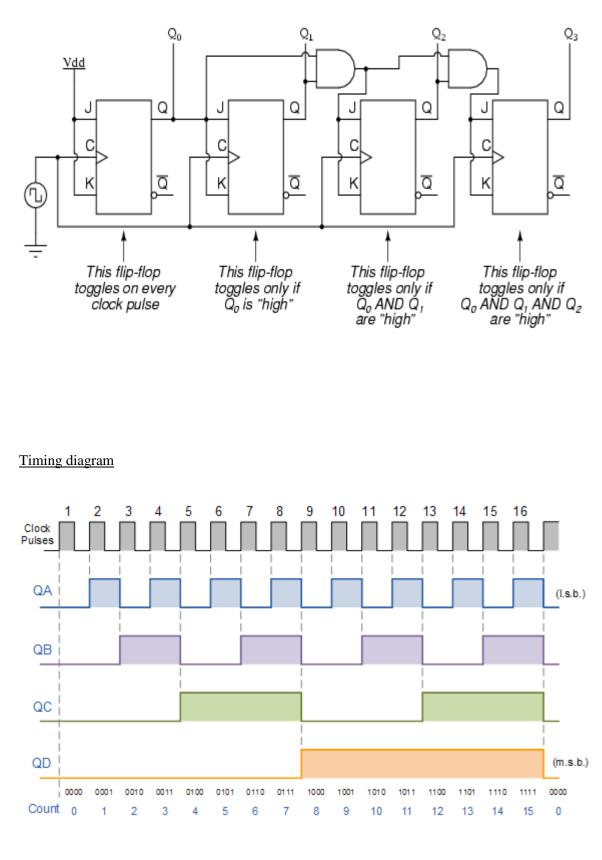

The term asynchronous refers to events that do not occur at the same time. With respect to counter operation, asynchronous means that the flip-flops within the counter are not connected in a way to cause all flip-flops at exactly the same time. They are wired in a way that links the clock of the next flip-flop to the Q of the current device. This causes the output count states to the ripple through the counter. A counter is a circuit that produces a set of unique output combinations corresponding to the number of applied input pulses. The number of unique outputs of a counter is known as its modulus or mod number. Each flip flop is triggered by the output from the previous flip flop expect for the first flip flop (LSB) which receives an external clock. Asynchronous counters are commonly referred to as ripple counters because the effect of the input clock pulse is first felt by FF0. This effect cannot get to FF1 immediately because of the propagation delay through FF0.

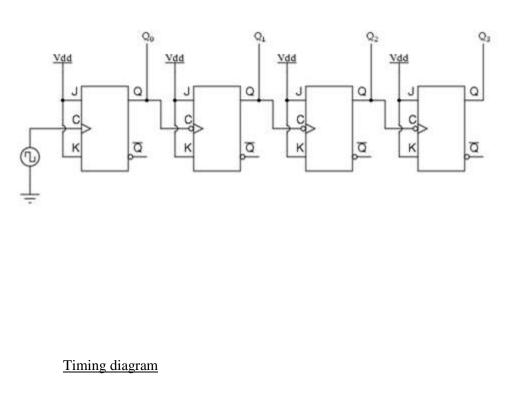

#### 4 bit asynchronous up-counter

An asynchronous 4 bit binary up counter, a circuit made up of 4 J-K flip-flop cascaded to generate four bits counting sequence. An up counter is basically a digital counting circuit which counts up in an incremental mode.

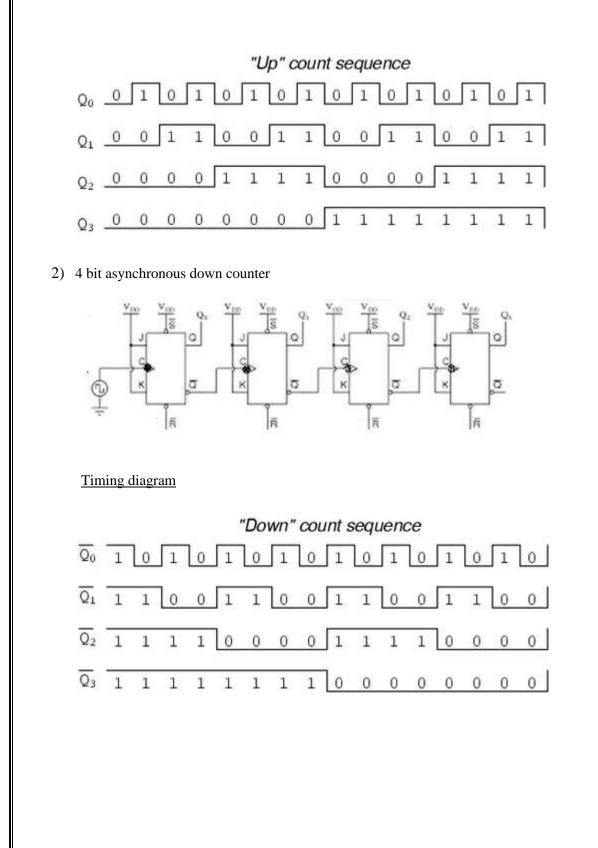

### 4 bit asynchronous down-counter.

An asynchronous 4 bit binary up counter, a circuit made up of 4 J-K flip-flop cascaded to generate four bits counting sequence. A down counter is basically a digital counting circuit which counts down in a decremental mode.

### Asynchronous decade counter

The modulus for counters for counters is the number of unique states through which the counter will sequence. The maximum possible number of states of a counter is 2<sup>n</sup>, where n is the number of flip flops in the counter. A decade counter with a count sequence of zero (0000) through nine (1001) is a BCD decade counter because its ten-state sequence produces the BCD code. This type of counter is useful in display applications in which BCD is required for conversion to a decimal readout.

### 3-bit up/down counter

The direction of counting is decided by a mode control input M.An XOR gate between flip flop functioning as a controlled inverter connects either of Q or Q bar to the clock input of the succeeding flip flop as decided by the logic state at M.When mode control is 0,Q outputs get connected to the clock inputs of the succeeding flip flop and counter counts up. When mode control is 1, Qbar outputs are connected to the clock inputs and counter counts down.

### **CIRCUIT DIAGRAM AND DESIGN:**

1) 4 bit asynchronous up-counter

### 3) Decade counter

### **EXPERIMENT:**

### Procedure

- 1) Place the IC on IC Trainer Kit.

- 2) Connect  $V_{CC}$  and ground to respective pins of IC Trainer Kit.

- 3) Connect the inputs to the input switches provided in the IC Trainer Kit.

- 4) Connect the outputs to the switches of output LEDs

- 5) Apply various combinations of inputs according to the truth table and observe condition of LEDs

### **OBSERVATIONS:**

# Truth table

1) 4 bit asynchronous up-counter

| Clock | Q3 | Q2 | <b>Q1</b> | <b>Q0</b> |

|-------|----|----|-----------|-----------|

| 1     | 0  | 0  | 0         | 0         |

| 2     | 0  | 0  | 0         | 1         |

|       | 0  | 0  | 1         | 0         |

| 4     | 0  | 0  | 1         | 1         |

| 5     | 0  | 1  | 0         | 0         |

| 6     | 0  | 1  | 0         | 1         |

| 7     | 0  | 1  | 1         | 0         |

| 8     | 0  | 1  | 1         | 1         |

| 9     | 1  | 0  | 0         | 0         |

| 10    | 1  | 0  | 0         | 1         |

| 11    | 1  | 0  | 1         | 0         |

| 12    | 1  | 0  | 1         | 1         |

| 13    | 1  | 1  | 0         | 0         |

| 14    | 1  | 1  | 0         | 1         |

| 15    | 1  | 1  | 1         | 0         |

| 16    | 1  | 1  | 1         | 1         |

3) 4 bit asynchronous down-counter

| СК | Q, | Q <sub>2</sub> | Q <sub>1</sub> | Qo |

|----|----|----------------|----------------|----|

| 0  | 1  | 1              | 1              | 1  |

| 1  | 1  | 1              | 1              | 0  |

| 2  | 1  | 1              | 0              | 1  |

| 3  | 1  | 1              | 0              | 0  |

| 4  | 1  | 0              | 1              | 1  |

| 5  | 1  | 0              | 1              | 0  |

| 6  | 1  | 0              | 0              | 1  |

| 7  | 1  | 0              | 0              | 0  |

| 8  | 0  | 1              | 1              | 1  |

| 9  | 0  | 1              | 1              | 0  |

| 10 | 0  | 1              | 0              | 1  |

| 11 | 0  | 1              | 0              | 0  |

| 12 | 0  | 0              | 1              | 1  |

| 13 | 0  | 0              | 1              | 0  |

| 14 | 0  | 0              | 0              | 1  |

| 15 | 0  | 0              | 0              | 0  |

3) Decade counter

| Clock Pulse | Q3 | 02 | Q1 | QO |

|-------------|----|----|----|----|

| 0           | 0  | 0  | 0  | 0  |

| 1           | 0  | 0  | 0  | 1  |

| 2           | 0  | 0  | 1  | 0  |

| 3           | 0  | 0  | 1  | 1  |

| 4           | 0  | 1  | 0  | 0  |

| 5           | 0  | 1  | 0  | 1  |

| 6           | 0  | 1  | 1  | 0  |

| 7           | 0  | 1  | 1  | 1  |

| 8           | 1  | 0  | 0  | 0  |

| 9           | 1  | 0  | 0  | 1  |

4) 3-bit up/down counter using mode control

| CLK | Μ | <b>Q</b> <sub>2</sub> | <b>Q</b> 1 | Q <sub>0</sub> |

|-----|---|-----------------------|------------|----------------|

| 0   | 1 | 0                     | 0          | Q0<br>0        |

| 1   | 1 | 1                     | 1          | 1              |

| 2   | 1 | 1                     | 1          | 0              |

| 3   | 1 | 1                     | 0          | 1              |

| 4   | 1 | 1                     | 0          | 0              |

| 5   | 1 | 0                     | 1          | 1              |

| 6   | 1 | 0                     | 1          | 0              |

| 7   | 1 | 0                     | 0          | 1              |

| 8   | 1 | 0                     | 0          | 0              |

| 9   | 0 | 0                     | 0          | 1              |

| 10  | 0 | 0                     | 1          | 0              |

| 11  | 0 | 0                     | 1          | 1              |

| 12  | 0 | 1                     | 0          | 0              |

| 13  | 0 | 1                     | 0          | 1              |

| 14  | 0 | 1                     | 1          | 0              |

| 15  | 0 | 1                     | 1          | 1              |

# CONCLUSION

Asynchronous counters are designed and outputs are obtained.

LAB RECORD: LOGIC DESIGN LAB

#### EXPI NO: 9

DATE: \_\_/\_\_/\_\_

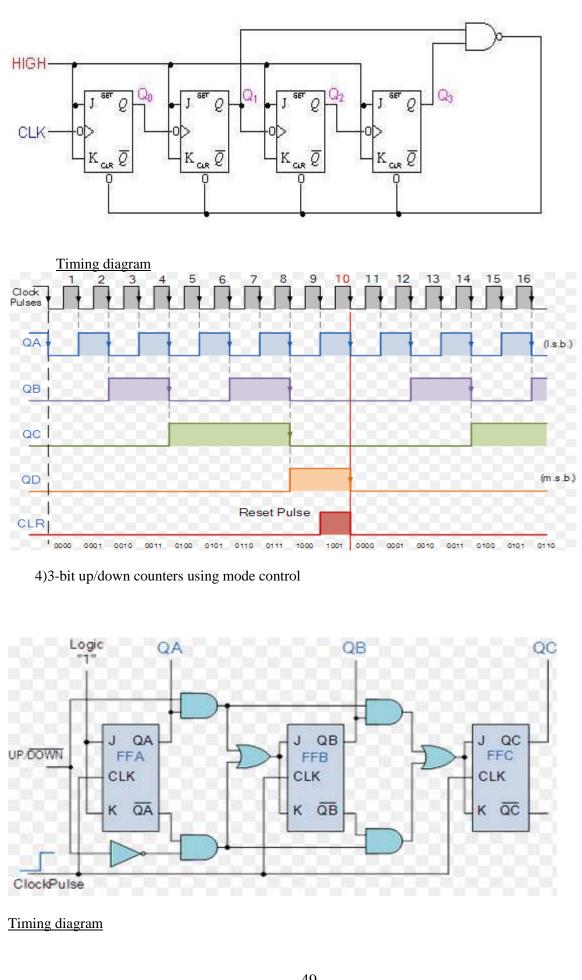

### SYNCHRONOUS COUNTERS

#### **OBJECTIVE:**

Realization of following synchronous counters

- (1) 4 bit Synchronous Counter

- (2) Synchronous Mod-N counters

- (3) 3 bit synchronous up-down counter

### HARDWARE REQUIRED:

| SLNo. | Components/Equipments | Specification | Quantity |

|-------|-----------------------|---------------|----------|

| 1.    | Digital Trainer Kit   |               | 1        |

| 2.    | IC                    | 7476          | 1        |

|       |                       | 7400          | 1        |

|       |                       | 7408          | 1        |

### **INTRODUCTION:**

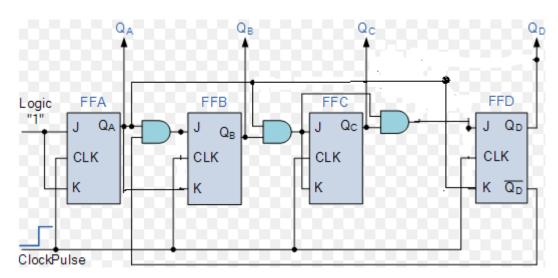

#### Synchronous counter

A synchronous **counter**, in contrast to an asynchronous **counter**, is one whose output bits change state simultaneously, with no ripple. The only way we can build such a **counter** circuit from J-K flip-flops is to connect all the clock inputs together, so that each and every flip-flop receives the exact same clock pulse at the exact same.

### **Mod -N Counter**

A mod-n counter has n possible states .that means it counts from 0 to n and rolls over it.There must be a way to force the counter stops counting at n and roll over to 0.This is where the asynchronous inputs come into play. The asynchronous inputs can override the synchronous inputs and force the output either at high or low.

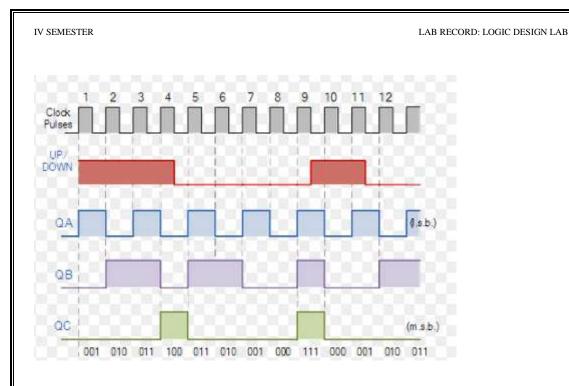

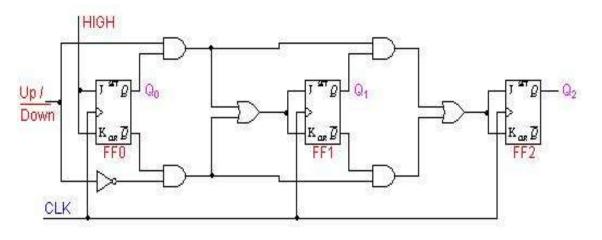

### 3 bit synchronous Up-down Counter

A counter is a register capable of counting number of clock pulse arriving at its clock input. Counter represents the number of clock pulses arrived. An up/down counter is one that is capable of progressing in increasing order or decreasing order through a certain sequence. An up/down counter is also called bidirectional counter. Usually up/down operation of the counter is controlled by up/down signal. When this signal is high counter goes through up sequence and when up/down signal is low counter follows reverse sequence.

# DESIGN, CIRCUIT DIAGRAM AND OBSERVATIONS:

### 1) 4 BIT SYNCHRONOUS UP COUNTER

Truth Table

| Clock<br>pulse | Present state |    |    |  |  |

|----------------|---------------|----|----|--|--|

|                | Q2            | Q1 | Q0 |  |  |

| 0              | 0             | 0  | 0  |  |  |

| 1              | 0             | 0  | 1  |  |  |

| 2              | 0             | 1  | 0  |  |  |

| 2 3            | 0             | 1  | 1  |  |  |

| 4              | 1             | 0  | 0  |  |  |

| 4<br>5         | 1             | 0  | 1  |  |  |

| 6              | 1             | 1  | 0  |  |  |

| 7              | 1             | 1  | 1  |  |  |

### Excitation Table

| Present | Next  | J3 | K3 | J2 | K2 | J1 | K1 | JO | KO |

|---------|-------|----|----|----|----|----|----|----|----|

| state   | state |    |    |    |    |    |    |    |    |

| 0000    | 0001  | 0  | Х  | 0  | X  | 0  | Х  | 1  | X  |

| 0001    | 0010  | 0  | Х  | 0  | X  | 1  | Х  | Х  | 1  |

| 0010    | 0011  | 0  | Х  | 0  | X  | Х  | 0  | 1  | Х  |

| 0011    | 0100  | 0  | Х  | 1  | X  | Х  | 1  | Х  | 1  |

| 0100    | 0101  | 0  | Х  | Х  | 0  | 0  | Х  | 1  | Х  |

| 0101    | 0110  | 0  | Х  | Х  | 0  | 1  | Х  | Х  | 1  |

| 0110    | 0111  | 0  | Х  | X  | 0  | X  | 0  | 1  | X  |

| 0111    | 1000  | 1  | Х  | Х  | 1  | Х  | 1  | Х  | 1  |

| 1000    | 1001  | Х  | 0  | 0  | X  | 0  | Х  | 1  | X  |

| 1001    | 1010  | Х  | 0  | 0  | X  | 1  | Х  | Х  | 1  |

| 1010    | 1011  | Х  | 0  | 0  | X  | Х  | 0  | 1  | Х  |

| 1011    | 1100  | Х  | 0  | 1  | X  | Х  | 1  | Х  | 1  |

| 1100    | 1101  | Х  | 0  | X  | 0  | 0  | Х  | 1  | X  |

| 1101    | 1110  | Х  | 0  | Х  | 0  | 1  | Х  | Х  | 1  |

| 1110    | 1111  | X  | 0  | X  | 0  | X  | 0  | 1  | X  |

| 1111    | 0000  | Х  | 1  | X  | 1  | X  | 1  | Х  | 1  |

| <u>K Maj</u><br>K-maps |    |    |    |    |                |    |   |

|------------------------|----|----|----|----|----------------|----|---|

| Q1 Q0<br>Q3 Q2         | 00 | 01 | 11 | 10 | Q1 Q0<br>Q3 Q2 | 00 | Τ |

| 00                     | 0  | 0  | 0  | 0  | 00             | x  | T |

| 01                     | 0  | 0  | 1  | 0  | 01             | x  | Т |

| 11                     | x  | x  | x  | Х  | 11             | 0  | t |

| 10                     | x  | х  | х  | x  | 10             | 0  | Т |

| Q1 Q0<br>Q3 Q2 | 00 | 01 | 11 | 10 |

|----------------|----|----|----|----|

| 00             | x  | х  | x  | X  |

| 01             | x  | Х  | x  | x  |

| 11             | 0  | 0  | 1  | 0  |

| 10             | 0  | 0  | 0  | 0  |

$J_3 = Q_2 Q_1 Q_0$

$K_3 = Q_2 Q_1 Q_0$

| $\begin{array}{c} Q_1Q_0\\ Q_3Q_2 \end{array}$ | 00 | 01 | 11 | 10 |

|------------------------------------------------|----|----|----|----|

| 00                                             | 0  | 0  | 1  | 0  |

| 01                                             | Х  | X  | Х  | X  |

| 11                                             | Х  | Х  | Х  | Х  |

| 10                                             | 0  | 0  | 1  | 0  |

$J_2 = Q_1 Q_0$

| $\begin{array}{c} Q_1 \ Q_0 \\ Q_3 \ Q_2 \end{array}$ | 00 | 01 | 11 | 10 |

|-------------------------------------------------------|----|----|----|----|

| 00                                                    | х  | х  | ×  | Х  |

| 01                                                    | 0  | 0  | 1  | 0  |

| 11                                                    | 0  | 0  | 1  | 0  |

| 10                                                    | X  | х  | X  | Х  |

$K_2 = Q_1 Q_0$

| Q1 Q0<br>Q3 Q2 | 00 | 01 | 11 | 10 |

|----------------|----|----|----|----|

| 00             | 0  | 1  | x  | X  |

| 01             | 0  | 1  | x  | х  |

| 11             | 0  | 1  | x  | x  |

| 10             | 0  | 1  | x  | x  |

| Q1 Q0<br>Q3 Q2 | 00 | 01 | 11 | 10  |

|----------------|----|----|----|-----|

| 00             | x  | *  | 1  | 0   |

| 01             | x  | ×  | 1  | 0   |

| 11             | x  | ×  | 1  | - 0 |

| 10             | x  | x  | 1  | 0   |

K1 = Q0

| $\begin{array}{c} Q_1 \ Q_0 \\ Q_3 \ Q_2 \end{array}$ | 00  | 01 | 11 | 10 |

|-------------------------------------------------------|-----|----|----|----|

| 00                                                    | 1   | 1  | 1  | 1  |

| 01                                                    | x   | ×  | x  | ×  |

| 11                                                    | -X- | х  | x  | X  |

| 10                                                    | 1   | 1  | 1  | 1  |

$J_0 = 1$

$J_1 = Q_0$

| Q1 Q0<br>Q3 Q2 | 00 | 01 | 11 | 10 |

|----------------|----|----|----|----|

| 00             | x  | ×  | x  | X  |

| 01             | 1  | 1  | 1  | 1  |

| 11             | 1  | 1  | 1  | 1  |

| 10             | x  | ×  | ×  | x  |

K<sub>0</sub> = 1

### Circuit daigram

## 2) 3 BIT SYNCHRONOUS UP/DOWN COUNTER

# <u>Truth Table</u>

| Clock<br>pulse | Present state |    |    |    |  |  |

|----------------|---------------|----|----|----|--|--|

| puise          | М             | Q2 | Q1 | Q0 |  |  |

| 0              | 1             | 0  | 0  | 0  |  |  |

| 1              | 1             | 0  | 0  | 1  |  |  |

| 1<br>2<br>3    | 1             | 0  | 1  | 0  |  |  |

| 3              | 1             | 0  | 1  | 1  |  |  |

| 4              | 1             | 1  | 0  | 0  |  |  |

| 5              | 1             | 1  | 0  | 1  |  |  |

| 6              | 1             | 1  | 1  | 0  |  |  |

| 7              | 1             | 1  | 1  | 1  |  |  |

| 8              | 0             | 1  | 1  | 1  |  |  |

| 9              | 0             | 1  | 1  | 0  |  |  |

| 10             | 0             | 1  | 0  | 1  |  |  |

| 11             | 0             | 1  | 0  | 0  |  |  |

| 12             | 0             | 0  | 1  | 1  |  |  |

| 13             | 0             | 0  | 1  | 0  |  |  |

| 14             | 0             | 0  | 0  | 1  |  |  |

| 15             | 0             | 0  | 0  | 0  |  |  |

**Excitation Table**

| Clock | Pre | sent s | tate |    | Next | t state |    | Inpu | ıts To     | Flipf | ops |    |    |

|-------|-----|--------|------|----|------|---------|----|------|------------|-------|-----|----|----|

| pulse |     | 1      | 1    | 1  |      | 1       | r  |      | т <u> </u> | 1     | r   | 1  |    |

|       | Μ   | Q2     | Q1   | Q0 | Q2   | Q1      | Q0 | J2   | K2         | J1    | K1  | JO | K0 |

| 0     | 0   | 0      | 0    | 0  | 1    | 1       | 1  | 1    | Х          | 1     | Х   | 1  | Х  |

| 1     | 0   | 0      | 0    | 1  | 0    | 0       | 1  | 0    | Х          | 0     | Х   | 1  | Х  |

| 2     | 0   | 0      | 1    | 0  | 0    | 0       | 0  | 0    | Х          | 0     | Х   | Х  | 1  |

| 3     | 0   | 0      | 1    | 1  | 0    | 1       | 0  | 0    | Х          | 1     | Х   | Х  | 1  |

| 4     | 0   | 1      | 0    | 0  | 0    | 0       | 1  | 0    | Х          | Х     | 1   | 1  | Х  |

| 5     | 0   | 1      | 0    | 1  | 0    | 1       | 1  | 0    | Х          | Х     | 0   | 1  | Х  |

| 6     | 0   | 1      | 1    | 0  | 0    | 1       | 0  | 0    | Х          | Х     | 0   | Х  | 1  |

| 7     | 0   | 1      | 1    | 1  | 1    | 0       | 0  | 1    | Х          | Х     | 1   | Х  | 1  |

| 8     | 1   | 0      | 0    | 0  | 0    | 1       | 1  | Х    | 1          | 1     | Х   | 1  | Х  |

| 9     | 1   | 0      | 0    | 1  | 1    | 0       | 1  | Х    | 0          | 0     | Х   | 1  | Х  |

| 10    | 1   | 0      | 1    | 0  | 1    | 0       | 0  | Х    | 0          | 0     | Х   | Х  | 1  |

| 11    | 1   | 0      | 1    | 1  | 1    | 1       | 0  | Х    | 0          | 1     | Х   | Х  | 1  |

| 12    | 1   | 1      | 0    | 0  | 1    | 0       | 1  | Х    | 0          | Х     | 1   | 1  | Х  |

| 13    | 1   | 1      | 0    | 1  | 1    | 1       | 1  | Х    | 0          | Х     | 0   | 1  | Х  |

| 14    | 1   | 1      | 1    | 0  | 1    | 1       | 0  | Х    | 0          | Х     | 0   | Х  | 1  |

| 15    | 1   | 1      | 1    | 1  | 0    | 0       | 0  | Х    | 1          | Х     | 1   | Х  | 1  |

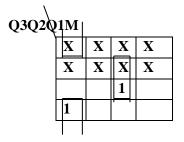

## K MAP:

# Q3Q2 \Q1M

| 1 |   |   |   |

|---|---|---|---|

|   |   | 1 |   |

| X | X | X | X |

| X | X | X | X |

|   |   |   | • |

## J3=Q2'Q1'M'+Q2Q1M

K3=Q2'Q1"M'+Q2Q1M

# Q3Q2 \Q1M

| 1- |   |   |   |

|----|---|---|---|

| 1  |   | 1 |   |

| X  | X | X | X |

| X  | Χ | X | Χ |

| 1  |   | 1 |   |

|    |   |   |   |

### J2=Q1'M'+Q1M

# Q3Q2 \Q1M

| X         | X | X | X |

|-----------|---|---|---|

| 1         |   | 1 |   |

| 1         |   | 1 |   |

| X         | X | X | X |

| $\square$ |   |   |   |

# K2=Q1'M'+Q1M

# Q3Q2 \Q1M

| 1         1         X           1         1         X | X |

|-------------------------------------------------------|---|

| 1 1 X                                                 | V |

|                                                       | Х |

| 1 1 X                                                 | Χ |

| 1 1 X                                                 | X |

J1=1

# Q3Q2 \Q1M

| X | X | 1 | 1 |

|---|---|---|---|

| X | X | 1 | 1 |

| X | X | 1 | 1 |

| X | X | 1 | 1 |

## K1=1

# <u>Circuit daigram</u>

# 3) Mod 10 synchronous counter

## <u>Truth Table</u>

| Clock Pulse   | Q3 | Q2 | Q1 | QO |

|---------------|----|----|----|----|

| Initially     | 0  | 0  | 0  | 0  |

| 1             | 0  | 0  | 0  | 1  |

| 2             | 0  | 0  | 1  | 0  |

| 3             | 0  | 0  | 1  | 1  |

| 4             | 0  | 1  | 0  | 0  |

| 5             | 0  | 1  | 0  | 1  |

| 6             | 0  | 1  | 1  | 0  |

| 7             | 0  | 1  | 1  | 1  |

| 8             | 1  | 0  | 0  | 0  |

| 9             | 1  | 0  | 0  | 1  |

| 10 (recycles) | 0  | 0  | 0  | 0  |

LAB RECORD: LOGIC DESIGN LAB

### Excitation table

|    | Preser | t State | e  |    | Next | state |    |    |    | Inp | uts To | Flipf | lops |    |    |

|----|--------|---------|----|----|------|-------|----|----|----|-----|--------|-------|------|----|----|

| Q3 | Q2     | Q1      | Q0 | Q3 | Q2   | Q1    | Q0 | J3 | K3 | J2  | K2     | J1    | K1   | JO | K0 |

| 0  | 0      | 0       | 0  | 0  | 0    | 0     | 1  | 0  | Х  | 0   | Х      | 0     | Х    | 1  | Х  |

| 0  | 0      | 0       | 1  | 0  | 0    | 1     | 0  | 0  | Х  | 0   | Х      | 1     | Х    | Х  | 1  |

| 0  | 0      | 1       | 0  | 0  | 0    | 1     | 1  | 0  | Х  | 0   | Х      | Х     | 0    | 1  | Х  |

| 0  | 0      | 1       | 1  | 0  | 1    | 0     | 0  | 0  | Х  | 1   | Х      | Х     | 1    | Х  | 1  |

| 0  | 1      | 0       | 0  | 0  | 1    | 0     | 1  | 0  | Х  | Х   | 0      | 0     | Х    | 1  | Х  |

| 0  | 1      | 0       | 1  | 0  | 1    | 1     | 0  | 0  | Х  | Х   | 0      | 1     | Х    | Х  | 1  |

| 0  | 1      | 1       | 0  | 0  | 1    | 1     | 1  | 0  | Х  | Х   | 0      | Х     | 0    | 1  | Х  |

| 0  | 1      | 1       | 1  | 1  | 0    | 0     | 0  | 1  | Х  | Х   | 1      | Х     | 1    | Х  | 1  |

| 1  | 0      | 0       | 0  | 1  | 0    | 0     | 1  | Х  | 0  | 0   | Х      | 0     | Х    | 1  | Х  |

| 1  | 0      | 0       | 1  | 0  | 0    | 0     | 0  | Х  | 1  | 0   | Х      | 0     | Х    | Х  | 1  |

### K MAP:

# Q4Q3 \Q2Q1

| <u>x-x</u>   |   |   |   |

|--------------|---|---|---|

| $\mathbf{r}$ |   |   |   |

|              |   | 1 |   |

| X            | X | X | X |

| X            | X | X | X |

# J4=Q3Q2Q1

# Q4Q3 \Q2Q1

| \ · · · · |   |   |   |

|-----------|---|---|---|

| `X        | X | X | X |

| X         | X | X | X |

| X         | X | X | X |

|           | 1 | X | X |

|           |   |   |   |

# K4=Q1

# Q4Q3 \Q2Q1

|   | • |   |   |

|---|---|---|---|

| Ì |   | 1 |   |

| X | X | X | X |

| X | X | X | X |

|   |   | X | X |

|   |   |   |   |

J3=Q2Q1

# Q4Q3 \Q2Q1

| v-v | . <b>-</b> |   |   |

|-----|------------|---|---|

| `X  | Х          | X | X |

|     |            | 1 |   |

| X   | Х          | X | X |

|     |            | X | X |

|     |            |   |   |

# K3=Q2Q1

# Q4Q3 \Q2Q1

|   | 1 | X | X |

|---|---|---|---|

|   | 1 | X | X |

| X | Х | Χ | X |

|   |   | X | X |

## J2=Q4'Q1

# Q3Q2 \Q1M

| X | X | 1 |   |

|---|---|---|---|

| X | X | 1 |   |

| X | X | X | X |

| X | X | Χ | X |

# K2=Q1

# Q4Q3 \Q2Q1

|    | - |   |   |

|----|---|---|---|

| `1 | Х | Х | 1 |

| 1  | X | X | 1 |

| X  | Х | Χ | X |

| 1  | X | X | X |

# J1=1

# Q4Q3 \Q2Q1

| \- · | - |   |   |

|------|---|---|---|

| `X   | 1 | 1 | Х |

| X    | 1 | 1 | X |

| Χ    | X | Χ | Χ |

| X    | 1 | X | X |

# K1=1

### Circuit daigram

### **EXPERIMENT:**

### Procedure

- 1. Place the IC on IC Trainer Kit.

- 2. Connect V<sub>CC</sub> and ground to respective pins of IC Trainer Kit.

- 3. Connect the inputs to the input switches provided in the IC Trainer Kit.

- 4. Connect the outputs to the switches of output LEDs

- 5. Apply various combinations of inputs according to the truth table and observe condition of LEDs

### CONCLUSION

The synchronous counters are designed and implemented.

LAB RECORD: LOGIC DESIGN LAB

### EXPI NO: 10

DATE: \_\_/\_\_/\_\_

### **RANDOM SEQUENCE GENERATOR**

### **OBJECTIVE:**

Realization of random sequence generator

### HARDWARE REQUIRED:

| SL | LNo. | Components/Equipments | Specification | Quantity |

|----|------|-----------------------|---------------|----------|

|    | 1.   | Digital Trainer Kit   |               | 1        |

|    | 2.   | IC                    | 7476          | 2        |

### **INTRODUCTION:**

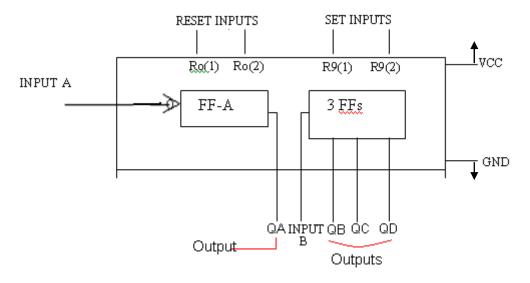

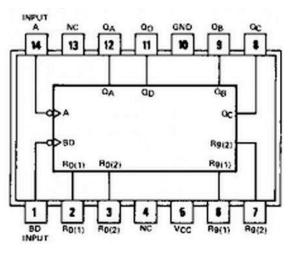

### Random sequence 1,2, 5, 7,.....

This counter has only four stable states, but it requires three Flipflops, because it counts 101 and 111. Three flips can have 8 states, out of which states 000,011,100,101 are invalid. The entries for excitations corresponding to invalid states are don't cares.

### **DESIGN and CIRCUIT DIAGRAM :**

### **Excitation Table**

| Present State Next State |    |    |    | Inp | uts to | Flip-flo | op |    |    |    |    |

|--------------------------|----|----|----|-----|--------|----------|----|----|----|----|----|

| Q2                       | Q1 | Q0 | Q2 | Q1  | Q0     | J2       | K2 | J1 | K1 | JO | K0 |

| 0                        | 0  | 1  | 0  | 1   | 0      | 0        | Х  | 1  | Х  | Х  | 1  |

| 0                        | 1  | 0  | 1  | 0   | 1      | 1        | Х  | Х  | 1  | 1  | Х  |

| 1                        | 0  | 1  | 1  | 1   | 1      | Х        | 0  | 1  | Х  | Х  | 0  |

| 1                        | 1  | 1  | 0  | 0   | 1      | Х        | 1  | Х  | 1  | Х  | 0  |

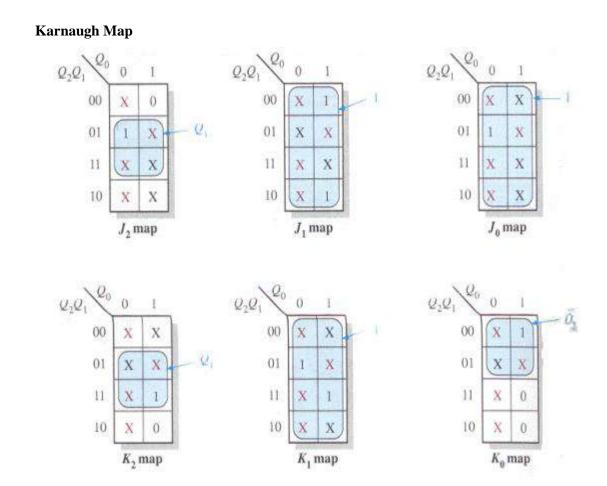

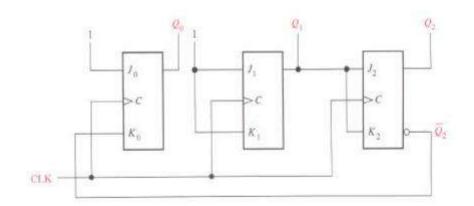

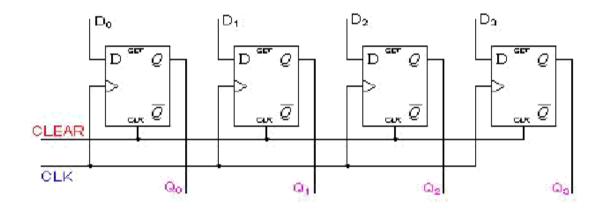

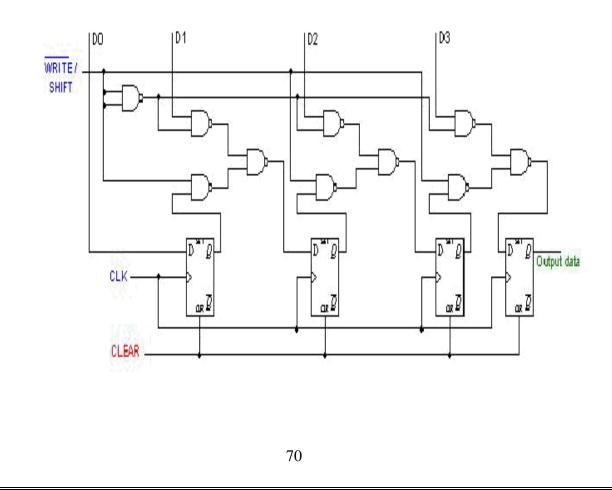

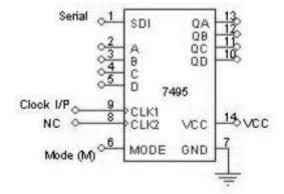

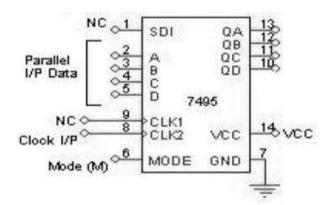

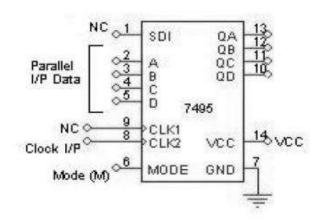

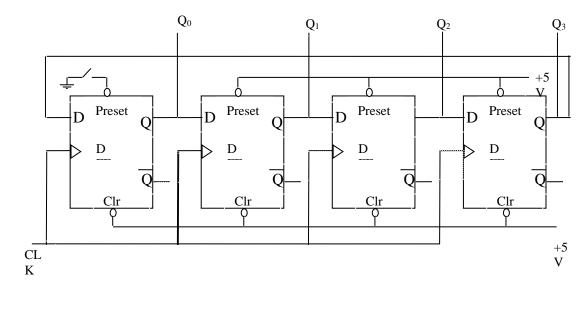

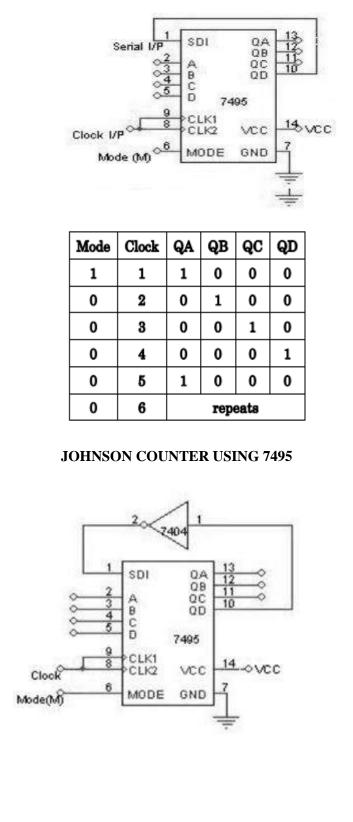

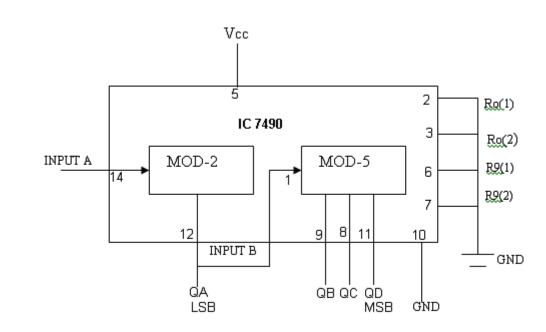

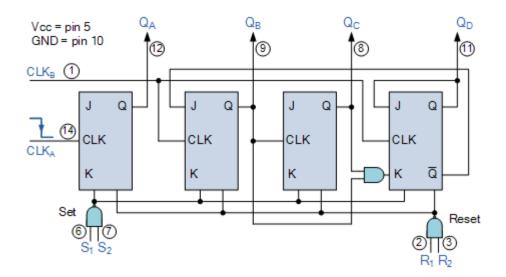

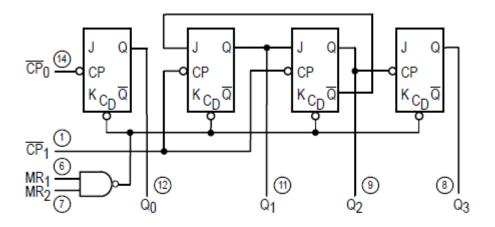

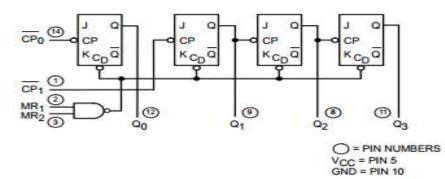

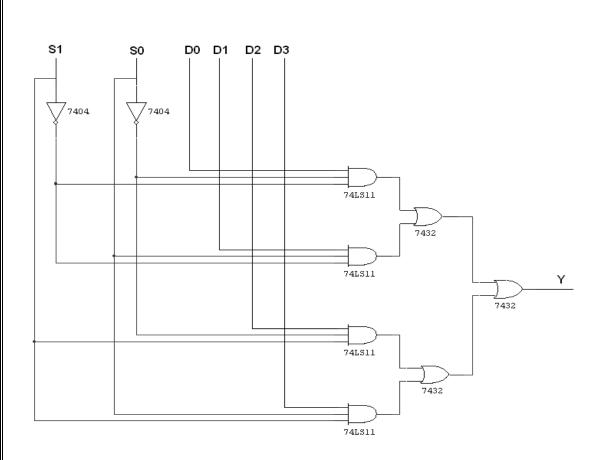

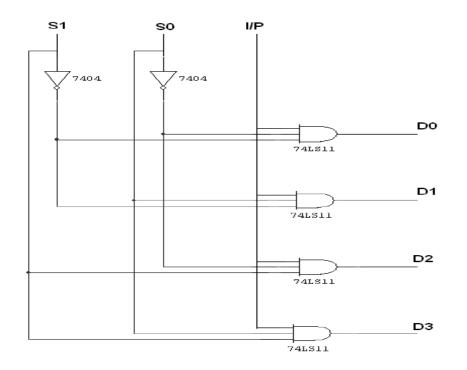

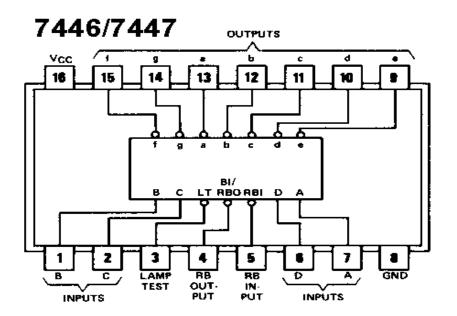

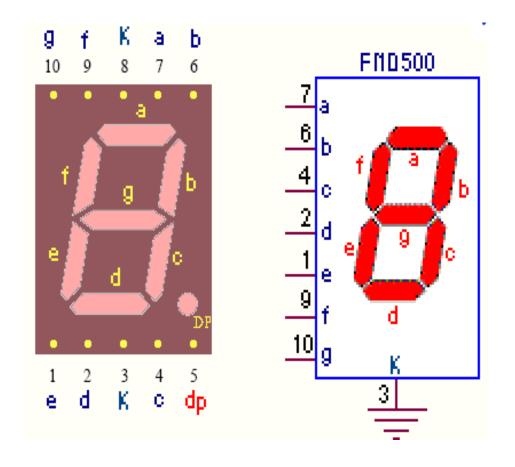

## Logic Expressions for Flip- flop Inputs